Appendix A

A-110 MIPS R4000 Microprocessor User's Manual

Format:

MFCz rt, rd

Description:

The contents of coprocessor register rd of coprocessor z are loaded into

general register rt.

Operation:

Exceptions:

Coprocessor unusable exception

*See the table “Opcode Bit Encoding” on next page, or “CPU Instruction

Opcode Bit Encoding” at the end of Appendix A.

MFCz

11

Move From Coprocessor

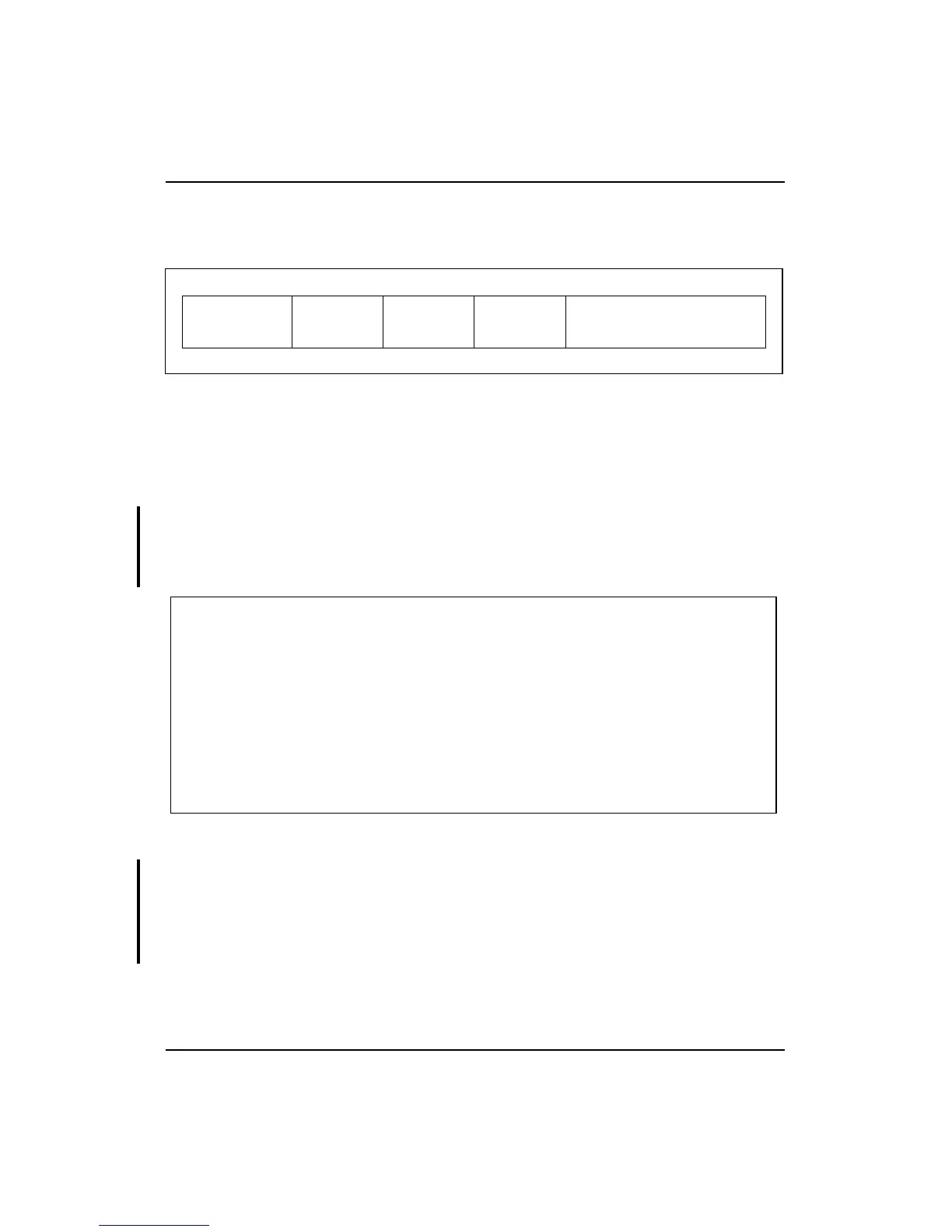

31 2526 2021 1516

COPz MF rt

655

rd

0

5

11 10 0

0 1 0 0 x x* 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

MFCz

32 T: data ← CPR[z,rd]

T+1: GPR[rt] ← data

64 T: if rd

0

= 0 then

data ← CPR[z,rd

4...1

|| 0]

31...0

else

data ← CPR[z,rd

4...1

|| 0]

63...32

endif

T+1: GPR[rt] ← (data

31

)

32

|| data

Loading...

Loading...