MIPS R4000 Microprocessor User's Manual A-141

CPU Instruction Set Details

Format:

SLLV rd, rt, rs

Description:

The contents of general register rt are shifted left the number of bits

specified by the low-order five bits contained in general register rs,

inserting zeros into the low-order bits.

The result is placed in register rd.

In 64-bit mode, the 32-bit result is sign extended when placed in the

destination register. It is sign extended for all shift amounts, including

zero; SLLV with a zero shift amount truncates a 64-bit value to 32 bits and

then sign extends this 32-bit value. SLLV, unlike nearly all other word

operations, does not require an operand to be a properly sign-extended

word value to produce a valid sign-extended word result.

NOTE: SLLV with a shift amount of zero may be treated as a NOP by

some assemblers, at some optimization levels. If using SLLV with a

zero shift to truncate 64-bit values, check the assembler you are using.

Operation:

Exceptions:

None

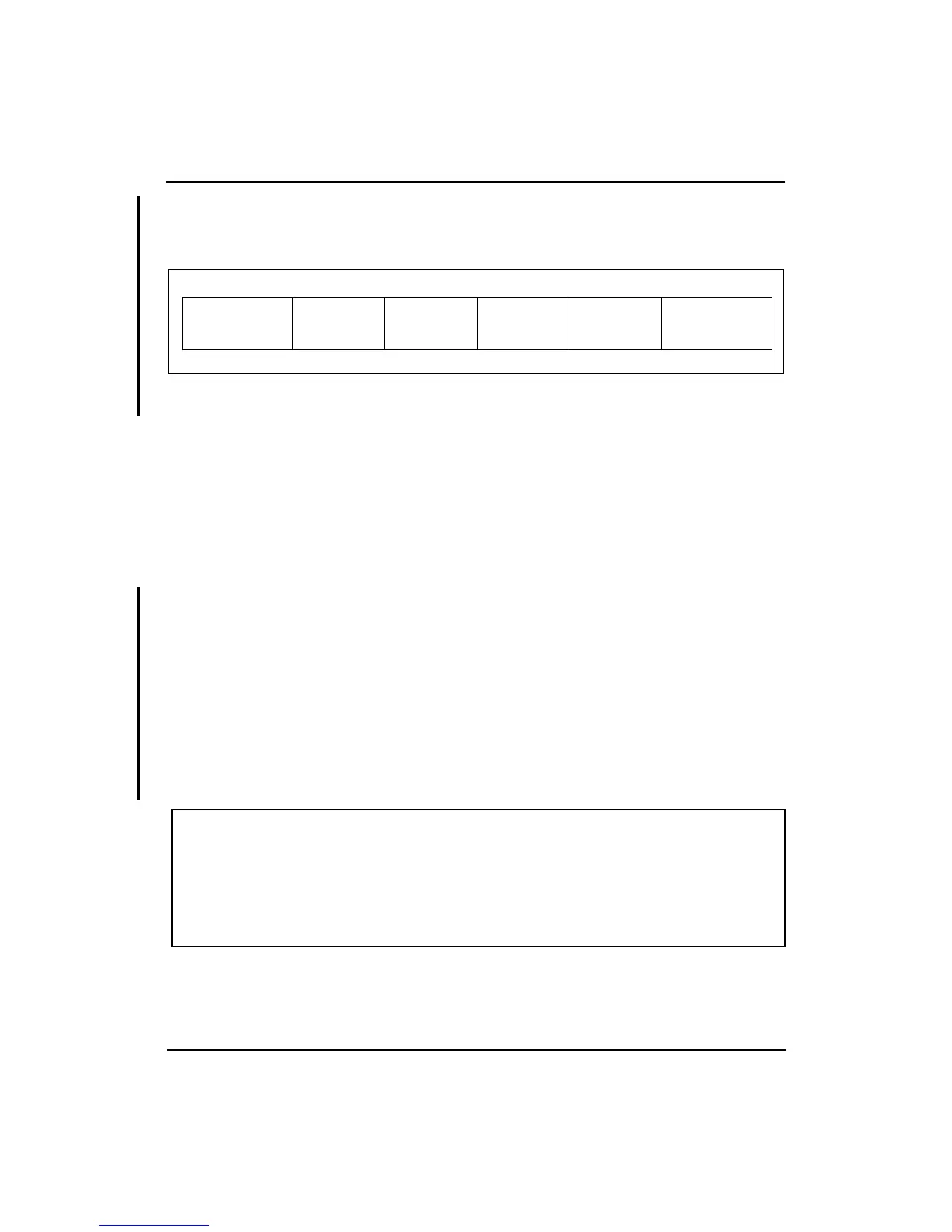

SLLV

Shift Left Logical Variable

31 2526 2021 1516

SPECIAL rt

655

rd 0 SLLV

55 6

11 10 6 5 0

0 0 0 0 0 0 0 0 0 1 0 00 0 0 0 0

SLLV

rs

32 T: s ← GP[rs]

4...0

GPR[rd]← GPR[rt]

(31–s)...0

|| 0

s

64 T: s ← 0 || GP[rs]

4...0

temp ← GPR[rt]

(31-s)...0

|| 0

s

GPR[rd] ← (temp

31

)

32

|| temp

Loading...

Loading...