Appendix B

B-8 MIPS R4000 Microprocessor User's Manual

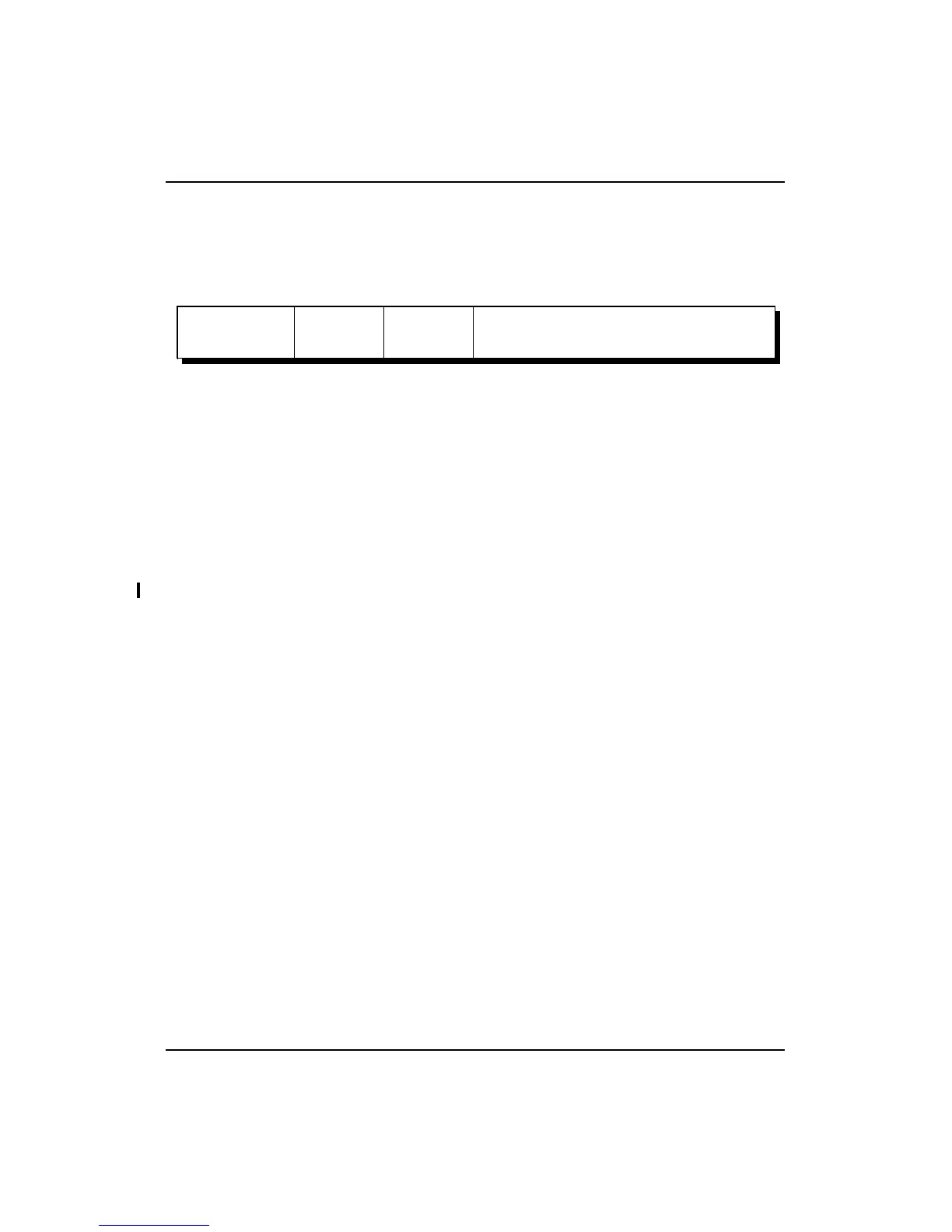

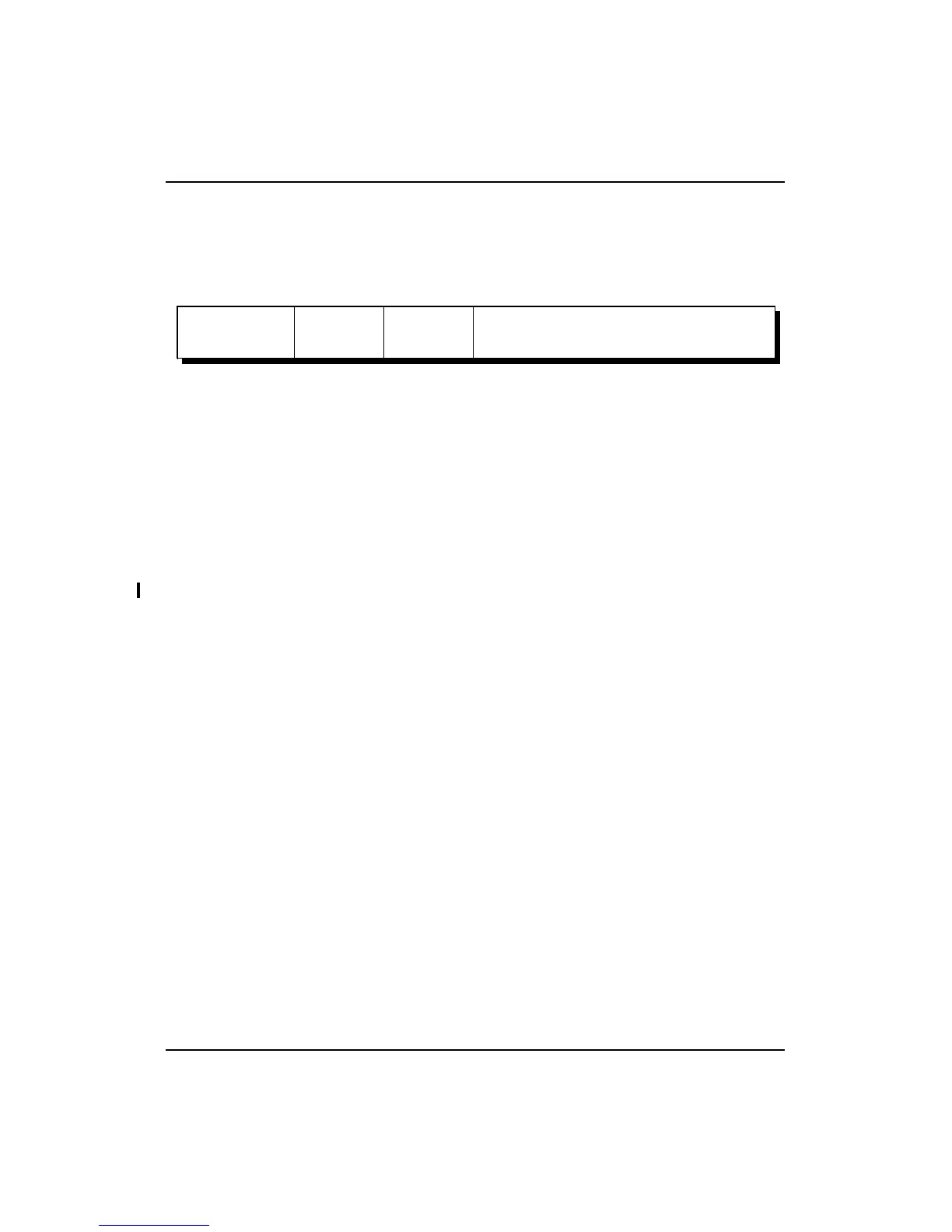

Figure B-1 shows the I-Type instruction format used by load and store

operations.

Figure B-1 Load and Store Instruction Format

All coprocessor loads and stores reference aligned data items. Thus, for

word loads and stores, the access type field is always WORD, and the low-

order two bits of the address must always be zero.

For doubleword loads and stores, the access type field is always

DOUBLEWORD, and the low-order three bits of the address must always

be zero.

Regardless of byte-numbering order (endianness), the address specifies

that byte which has the smallest byte-address in the addressed field. For

a big-endian machine, this is the leftmost byte; for a little-endian machine,

this is the rightmost byte.

op is a 6-bit operation code

base is the 5-bit base register specifier

ft

is a 5-bit source (for stores) or destination (for loads) FPA register

specifier

offset is the 16-bit signed immediate offset

31 25 21 20 16 0

I-Type (Immediate)

15

offset

26

ftbaseop

655 16

Loading...

Loading...