Appendix B

B-16 MIPS R4000 Microprocessor User's Manual

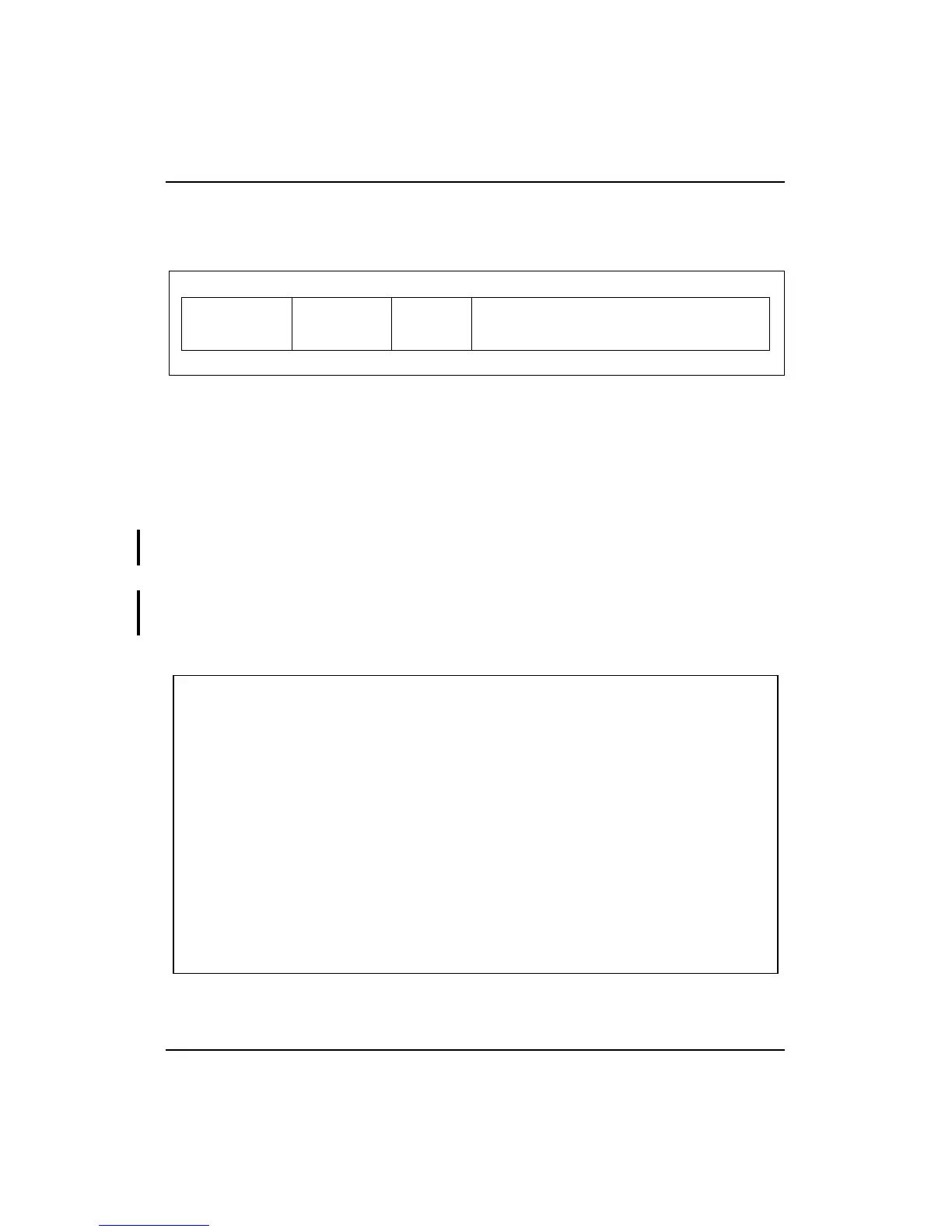

Format:

BC1FL offset

Description:

A branch target address is computed from the sum of the address of the

instruction in the delay slot and the 16-bit offset, shifted left two bits and

sign-extended. If the result of the last floating-point compare is false

(zero), the program branches to the target address, with a delay of one

instruction. If the conditional branch is not taken, the instruction in the

branch delay slot is nullified.

There must be at least one instruction between C.cond.fmt and BC1FL.

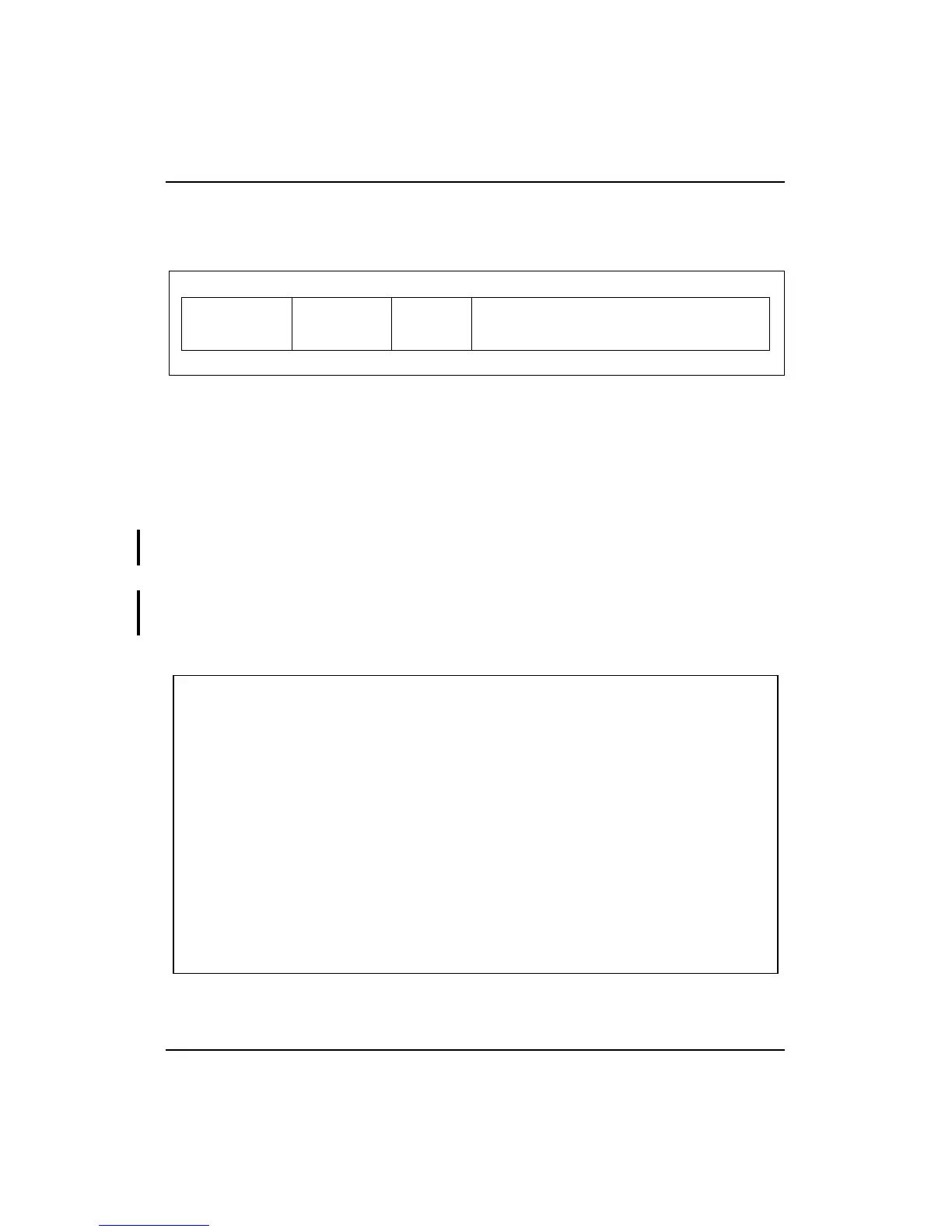

Operation:

Exceptions:

Coprocessor unusable exception

BC1FL

Branch On FPU False Likely

16 1531 2526

COP1

6

0

16

offset

(Coprocessor 1)

5

BC BCFL

5

21 20

0 1 0 0 0 1 0 1 0 0 0 0 0 0 1 0

BC1FL

64 T–1: condition ← not COC[1]

T: target ← (offset

15

)

46

|| offset || 0

2

T+1: if condition then

PC ← PC + target

else

NullifyCurrentInstruction

endif

32 T–1: condition ← not COC[1]

T: target ← (offset

15

)

14

|| offset || 0

2

T+1: if condition then

PC ← PC + target

else

NullifyCurrentInstruction

endif

Loading...

Loading...