MIPS R4000 Microprocessor User's Manual B-17

FPU Instruction Set Details

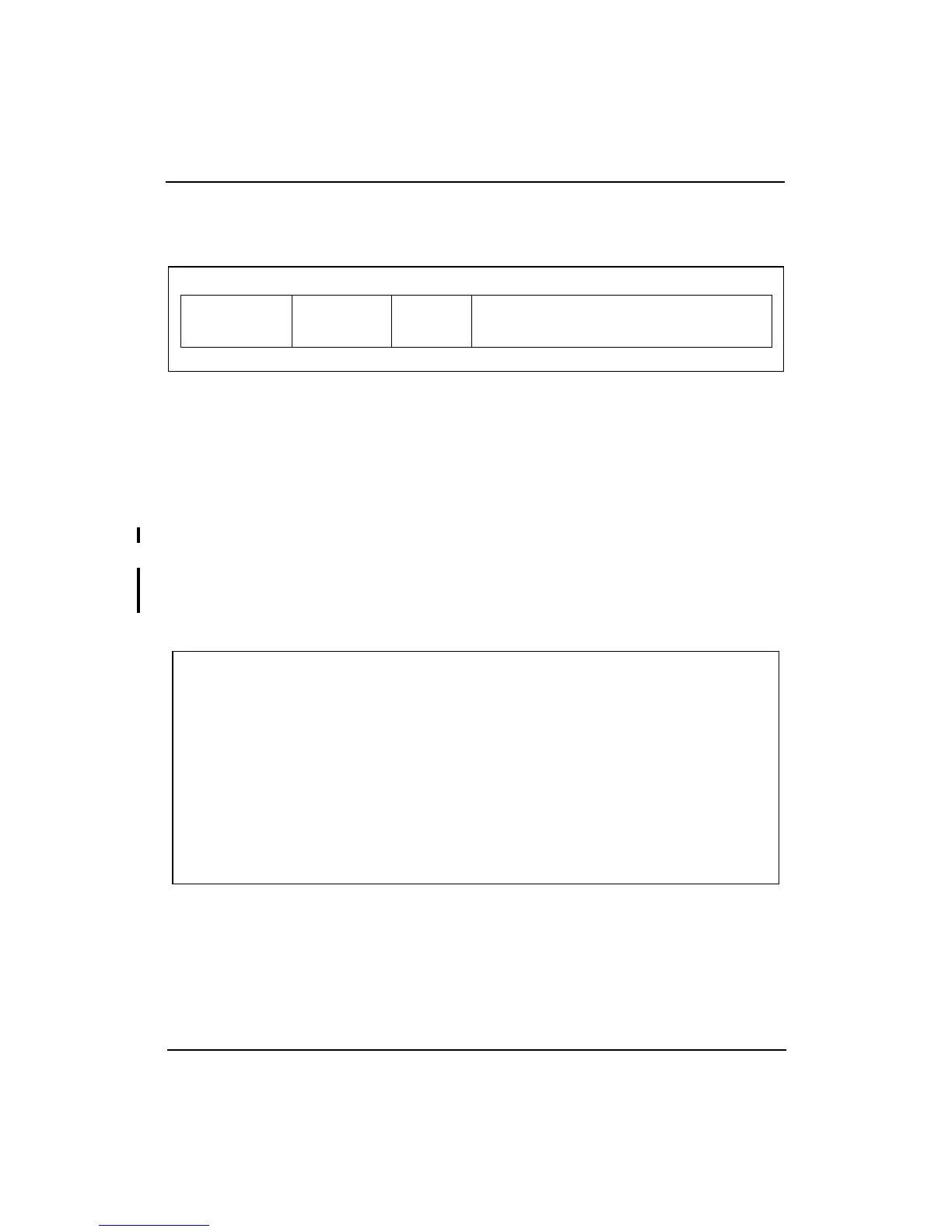

Format:

BC1T offset

Description:

A branch target address is computed from the sum of the address of the

instruction in the delay slot and the 16-bit offset, shifted left two bits and

sign-extended. If the result of the last floating-point compare is true (one),

the program branches to the target address, with a delay of one

instruction.

There must be at least one instruction between C.cond.fmt and BC1T.

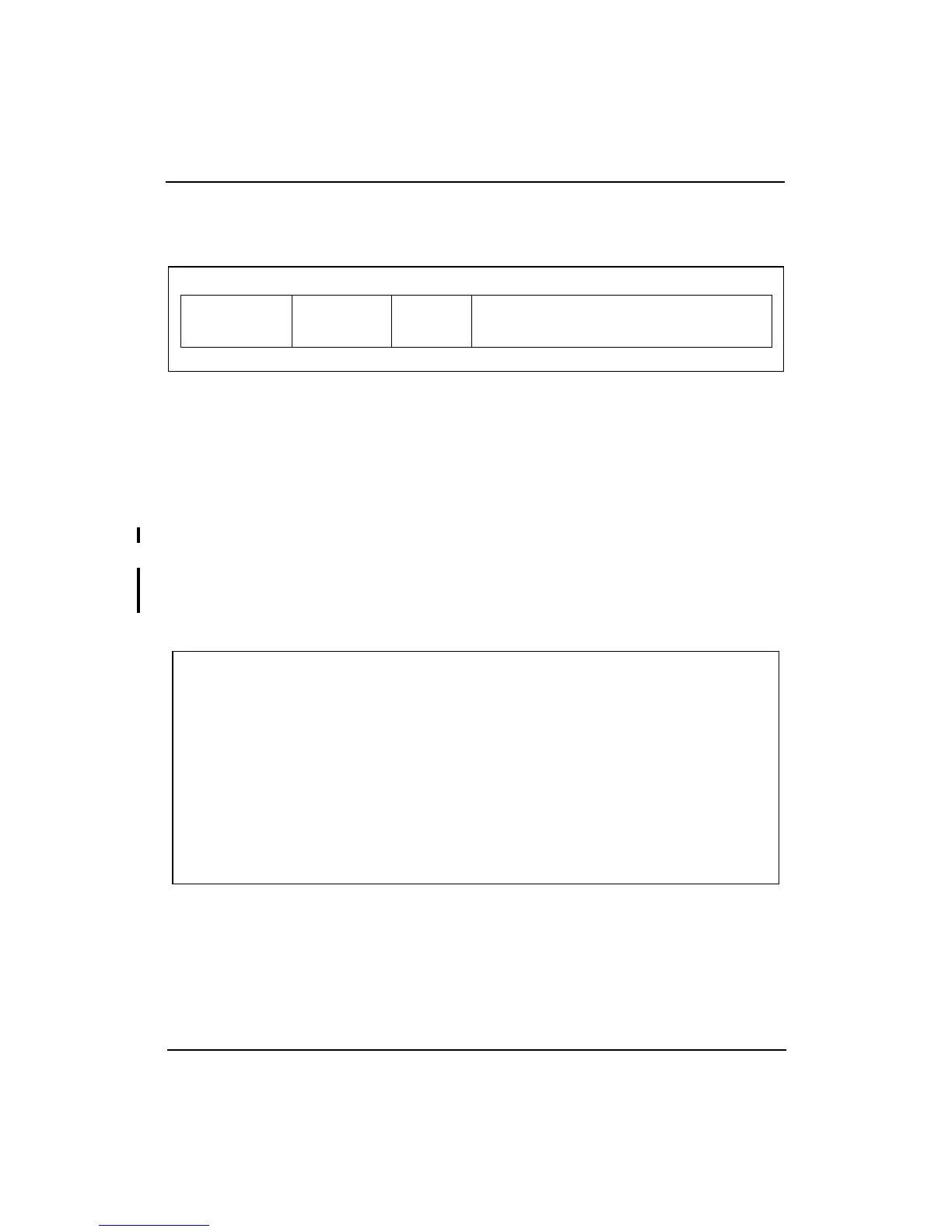

Operation:

Exceptions:

Coprocessor unusable exception

BC1T

Branch On FPU True

5

16 15

BC

31 2526

COP1

6

0

16

offset

(Coprocessor 1)

BCT

5

21 20

0 1 0 0 0 1 0 1 0 0 0 0 0 0 0 1

BC1T

32 T–1: condition ← COC[1]

T: target ← (offset

15

)

14

|| offset || 0

2

T+1: if condition then

PC ← PC + target

endif

64 T–1: condition ← COC[1]

T: target ← (offset

15

)

46

|| offset || 0

2

T+1: if condition then

PC ← PC + target

endif

Loading...

Loading...