Appendix F

F-4 MIPS R4000 Microprocessor User's Manual

β Only one instruction is needed to separate Index Load Tag and

MFC0 Tag, even though table timing indicates otherwise.

γ An MTC0 of a CPR must not be immediately followed by MFC0 of

the same CPR.

δ With an MTC0 to Status that modifies KSU and sets EXL or ERL, it

is possible for the five instructions following the MTC0 to be

executed incorrectly in the new mode, and not correctly in the

kernel mode. This can be avoided by setting EXL first, and only

later changing the value of KSU.

ε There must be two non-load, non-CACHE instructions between a

store and a CACHE instruction directed to the same primary cache

line as the store.

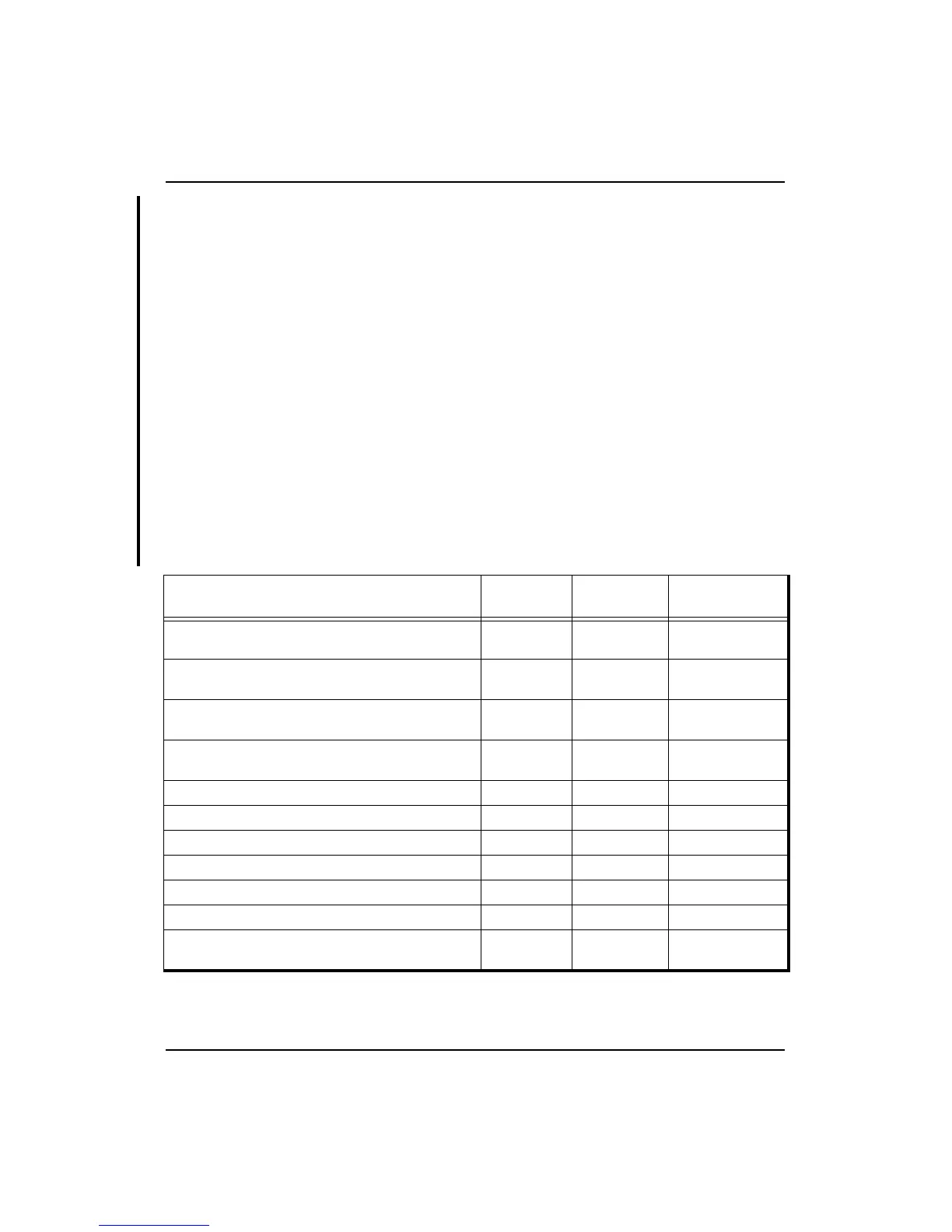

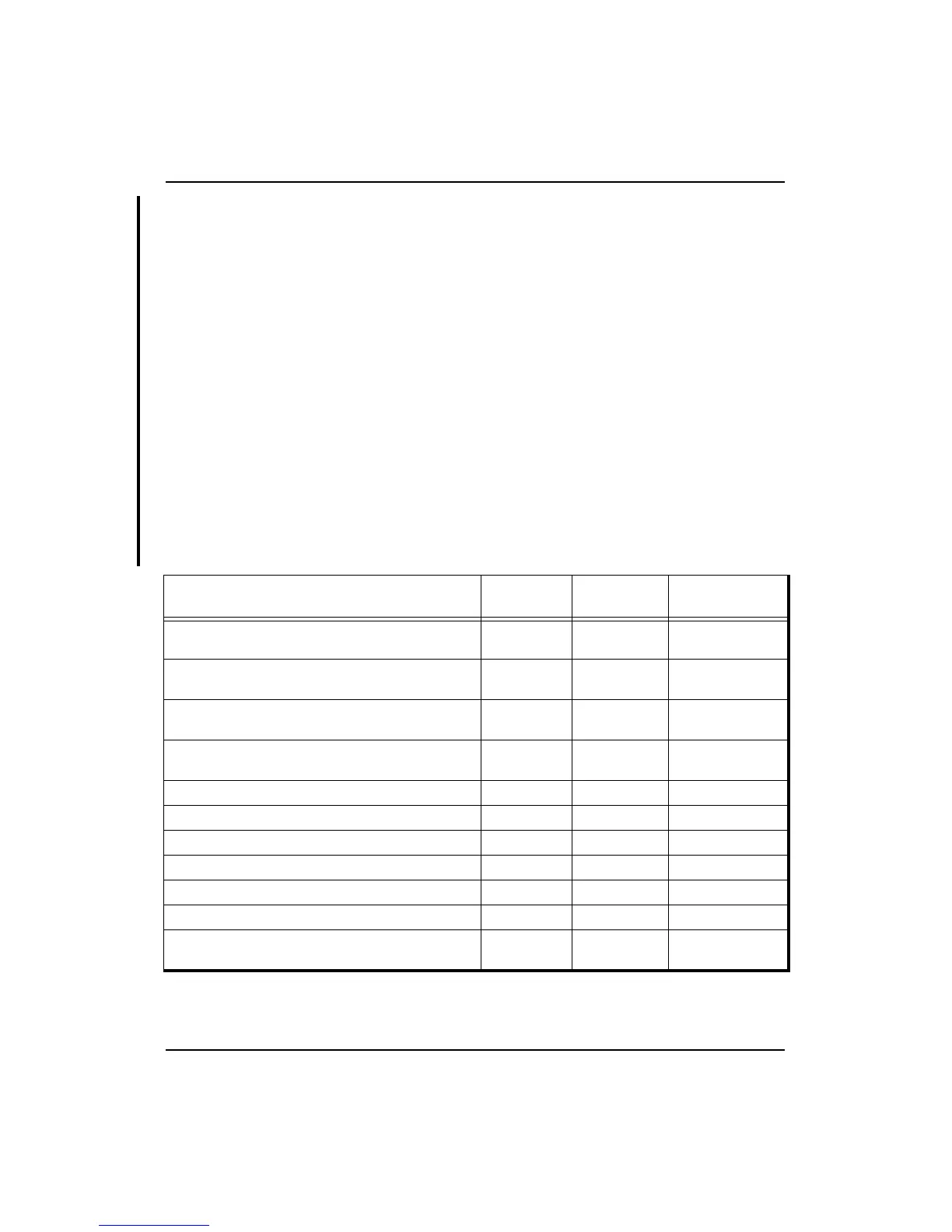

Table F-2 lists some hazard conditions, and the number of instructions that

must come between the writer and the user. The table shows the data item

that creates the hazard, and the calculation for the required number of

intervening instructions.

Table F-2 CP0 Hazards and Calculated Delay Times.

†. You cannot depend on a delay in effect if the instruction execution order is changed by exceptions.

In this case, for example, the minimum delay for IE to be effective is the maximum delay before a

pending, enabled interrupt can occur.

Writer → User Hazard On

Instructions

Between

Calculation

TLBWR/

TLBWI

→ TLBP TLB entry

3 8-(4+1)

TLBWR/

TLBWI

→

load/store using new TLB

entry

TLB entry

3 8-(4+1)

TLBWR/

TLBWI

→

I-fetch using new TLB

entry

TLB entry

5 8-(2+1)

MTCO

Status[CU]

→

Coprocessor instruction

needs CU set

Status[CU]

4 7-(2+1)

TLBR → MFC0 EntryHi EntryHi

3 8-(4+1)

MTC0 EntryLo0 → TLBWR/TLBWI EntryLo0

1 7-(5+1)

TLBP → MFC0 Index Index

2 7-(4+1)

MTC0 EntryHi → TLBP EntryHi

1 7-(5+1)

MTC0 EPC → ERET EPC

2 7-(4+1)

MTC0 Status → ERET Status

3 7-(3+1)

MTC0

Status[IE]

→ instruction interrupted

†

Status[IE]

3 7-(3+1)

Loading...

Loading...