MIPS R4000 Microprocessor User's Manual F-3

Coprocessor 0 Hazards

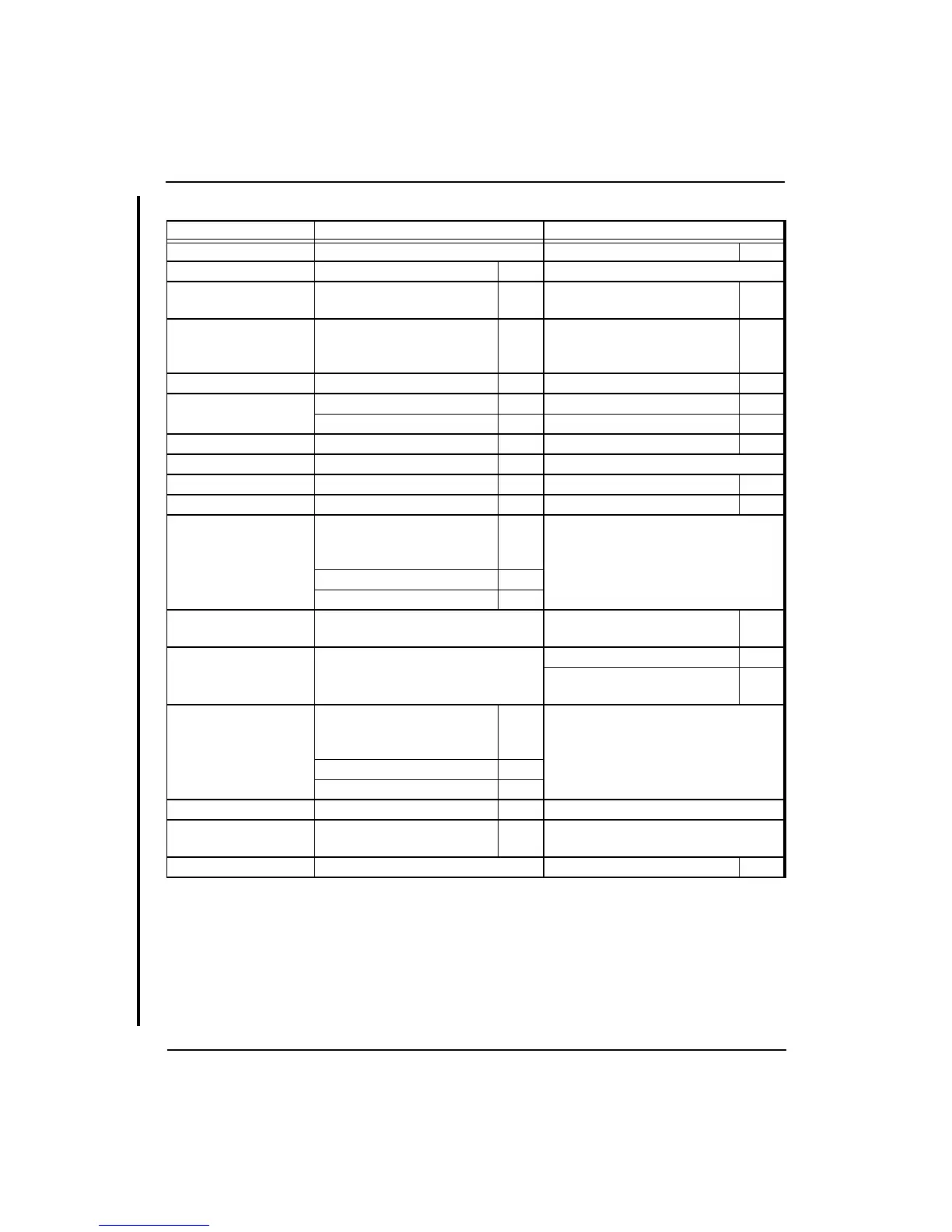

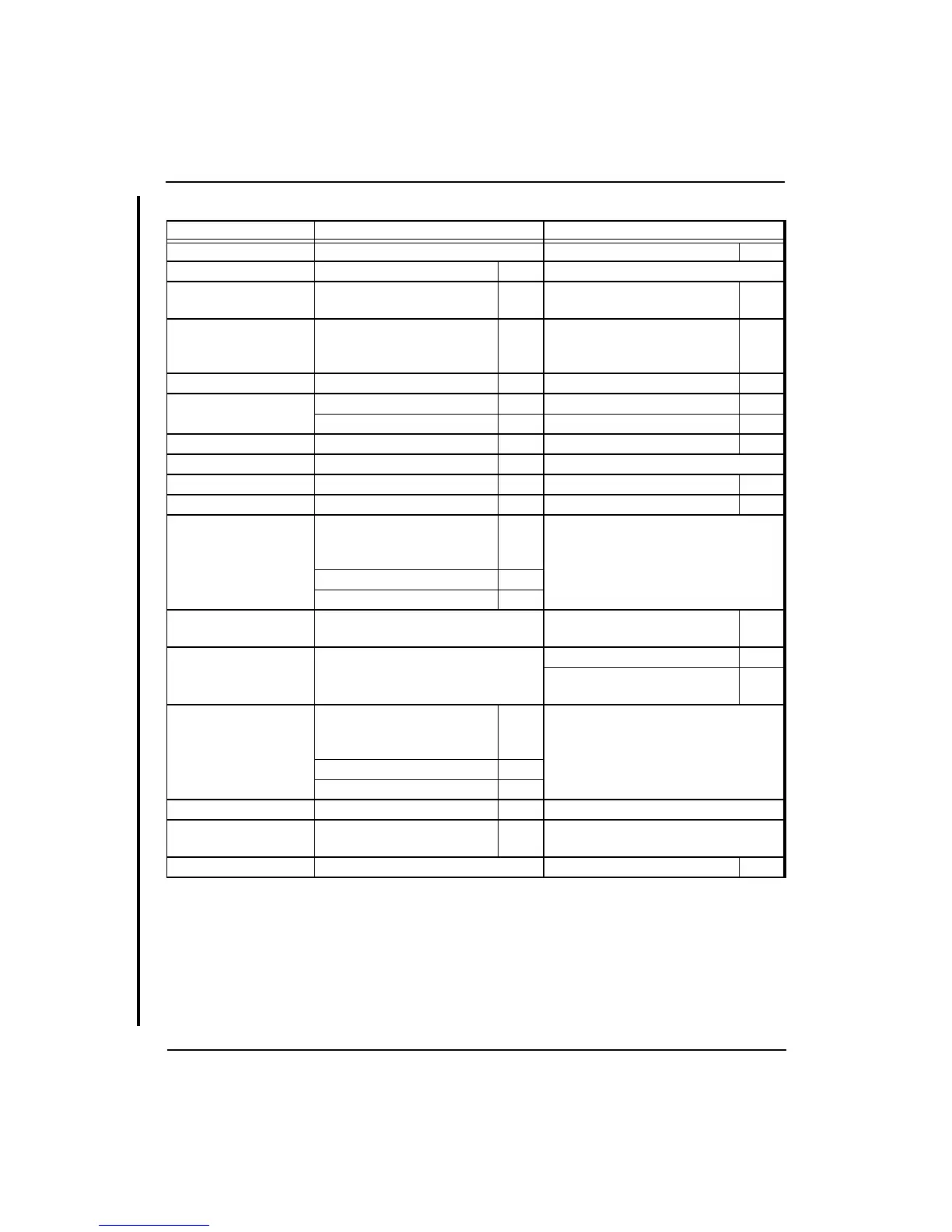

Table F-1 R4000 Coprocessor 0 Data Writer and User Timing

EntryHi.ASID refers to the ASID field of the EntryHi register.

Config[K0, DB] refers to the K0 and DB fields of the Config register.

α The EXL and ERL bits in the Status register are permanently

cleared in stage 8, if no exceptions abort the ERET. However the

effect of clearing them is visible to an instruction fetch starting in

stage 4, so the “returned to” instructions use the modified values in

the Status register.

Instruction or Event CP0 Data Used, Stage Used CP0 Data Written, Stage Available

MTC0 / DMTC0 CPR[0,rd] 7γδ

MFC0 / DMFC0 CPR[0,rd] 4βγ

TLBR Index, TLB 5-7

PageMask, EntryHi,

EntryLo0, EntryLo1

8

TLBWI

TLBWR

Index or Random,

PageMask, EntryHi,

EntryLo0, EntryLo1

5-8 TLB 8

TLBP PageMask, EntryHi 3-6 Index 7

ERET

EPC or ErrorEPC, TLB 4 Status[EXL, ERL] 4-8α

Status 3 LLbit 7

Index Load Tag TagLo, TagHi, ECC 8βε

Index Store Tag TagLo, TagHi, ECC 8ε

CACHE Hit ops Status[CH] 8ε

CACHE ops cache line (see note) ε cache line (see note) ε

Load/Store

EntryHi.ASID

Status[KSU, EXL, ERL, RE],

Config[K0, DB], TLB

4

Config[SB] 7

WatchHi, WatchLo 4-5

Load/Store exception

EPC, Status, Cause,

BadVaddr, Context, XContext

8

Instruction fetch

exception

EPC, Status 8

Cause, BadVAddr, Context,

XContext

4

Instruction fetch

EntryHi[ASID],

Status[KSU, EXL, ERL, RE],

Config[K0, IB]

0α

Config.SB 3

TLB (mapped addresses) 2

Coproc. usable test Status[CU, KSU, EXL, ERL] 2

Interrupt signals

sampled

Cause[IP],

Status[IM, IE, EXL, ERL]

3

TLB shutdown Status.TS 7

Loading...

Loading...