Appendix A

A-30 MIPS R4000 Microprocessor User's Manual

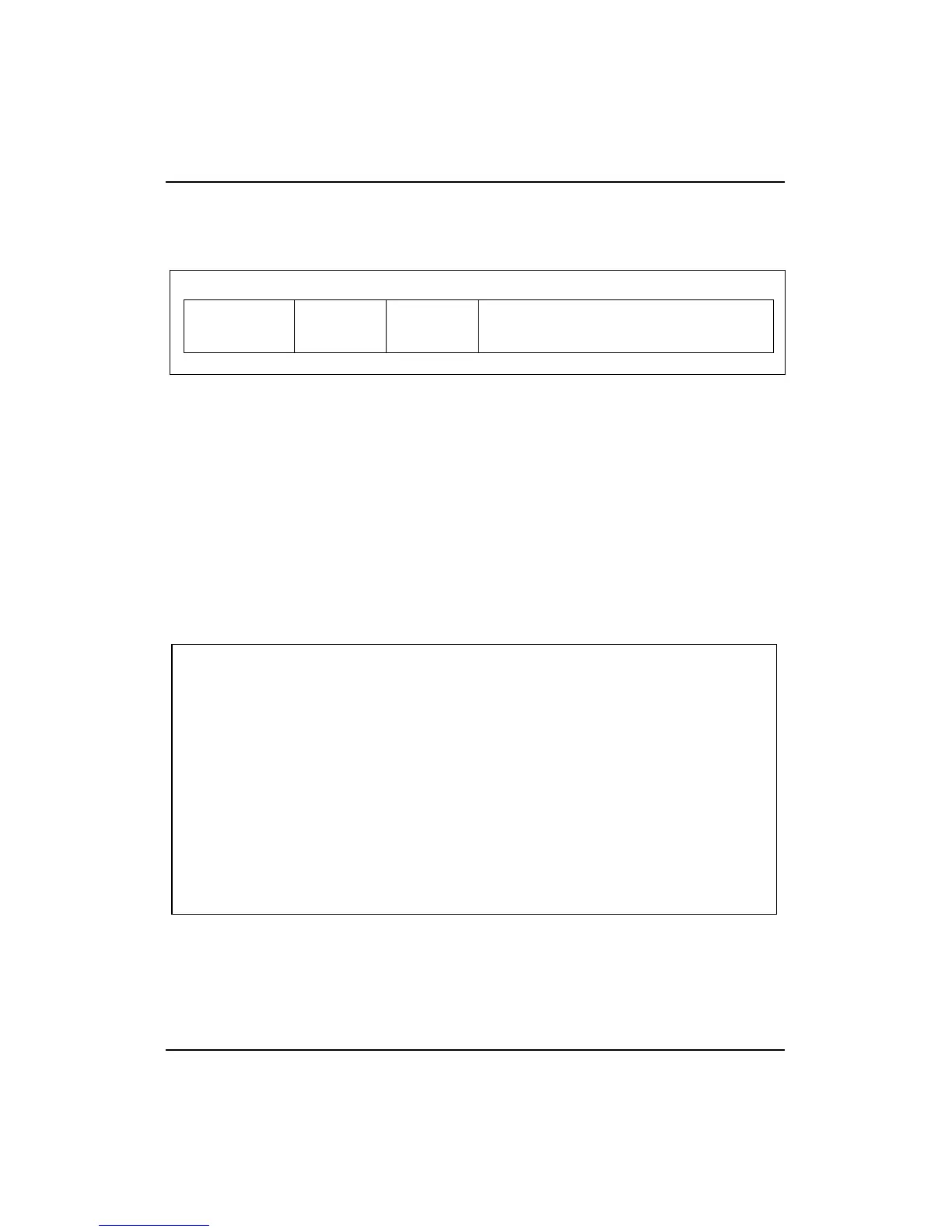

Format:

BGEZL rs, offset

Description:

A branch target address is computed from the sum of the address of the

instruction in the delay slot and the 16-bit offset, shifted left two bits and

sign-extended. If the contents of general register rs have the sign bit

cleared, then the program branches to the target address, with a delay of

one instruction. If the conditional branch is not taken, the instruction in

the branch delay slot is nullified.

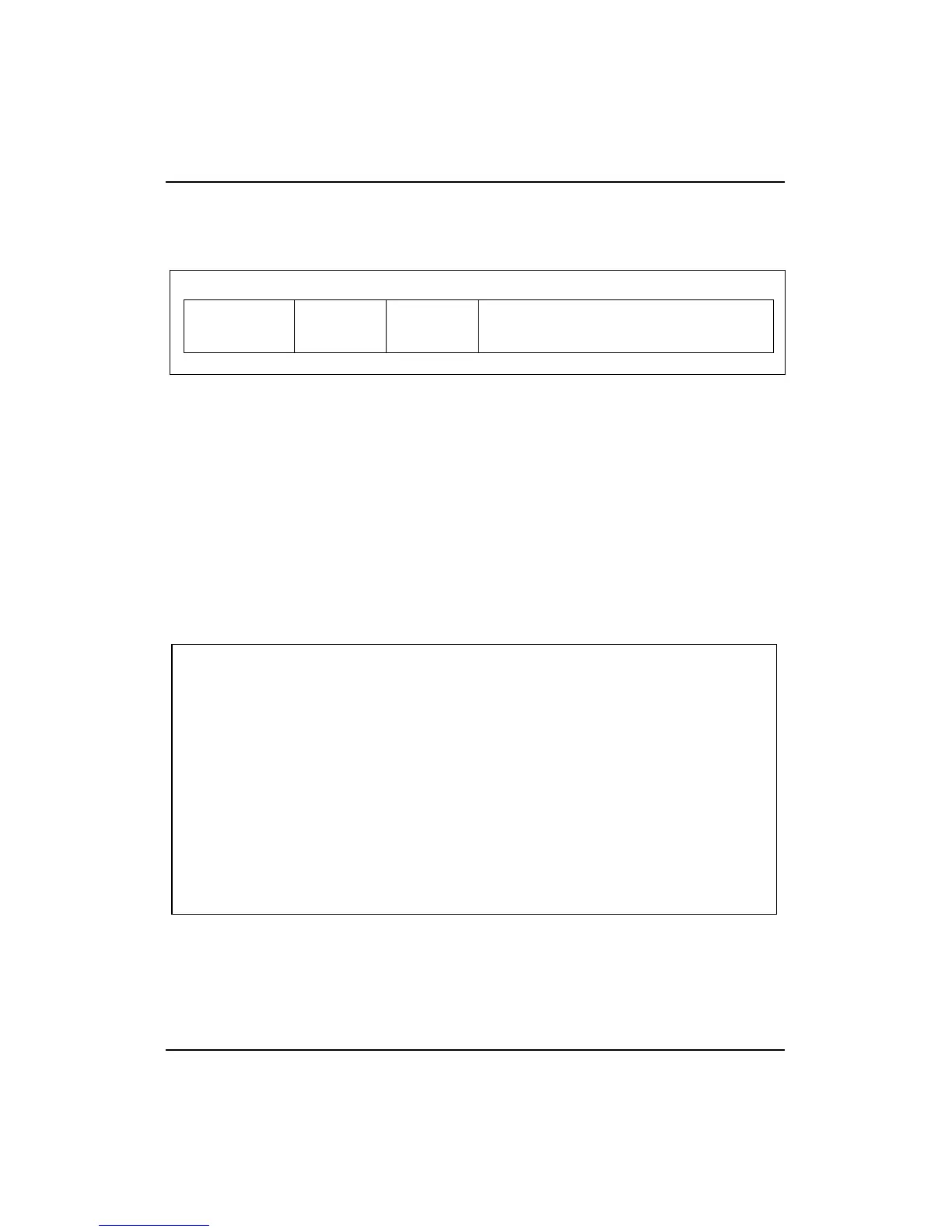

Operation:

Exceptions:

None

BGEZL

Than Or Equal To Zero Likely

Branch On Greater

31 2526 2021 1516 0

REGIMM rs BGEZL

offset

655 16

0 0 0 0 0 1 0 0 0 1 1

BGEZL

32 T: target ← (offset

15

)

14

|| offset || 0

2

condition ← (GPR[rs]

31

= 0)

T+1: if condition then

PC ← PC + target

endif

else

NullifyCurrentInstruction

64 T: target ← (offset

15

)

46

|| offset || 0

2

condition ← (GPR[rs]

63

= 0)

T+1: if condition then

PC ← PC + target

endif

else

NullifyCurrentInstruction

Loading...

Loading...