MIPS R4000 Microprocessor User's Manual A-31

CPU Instruction Set Details

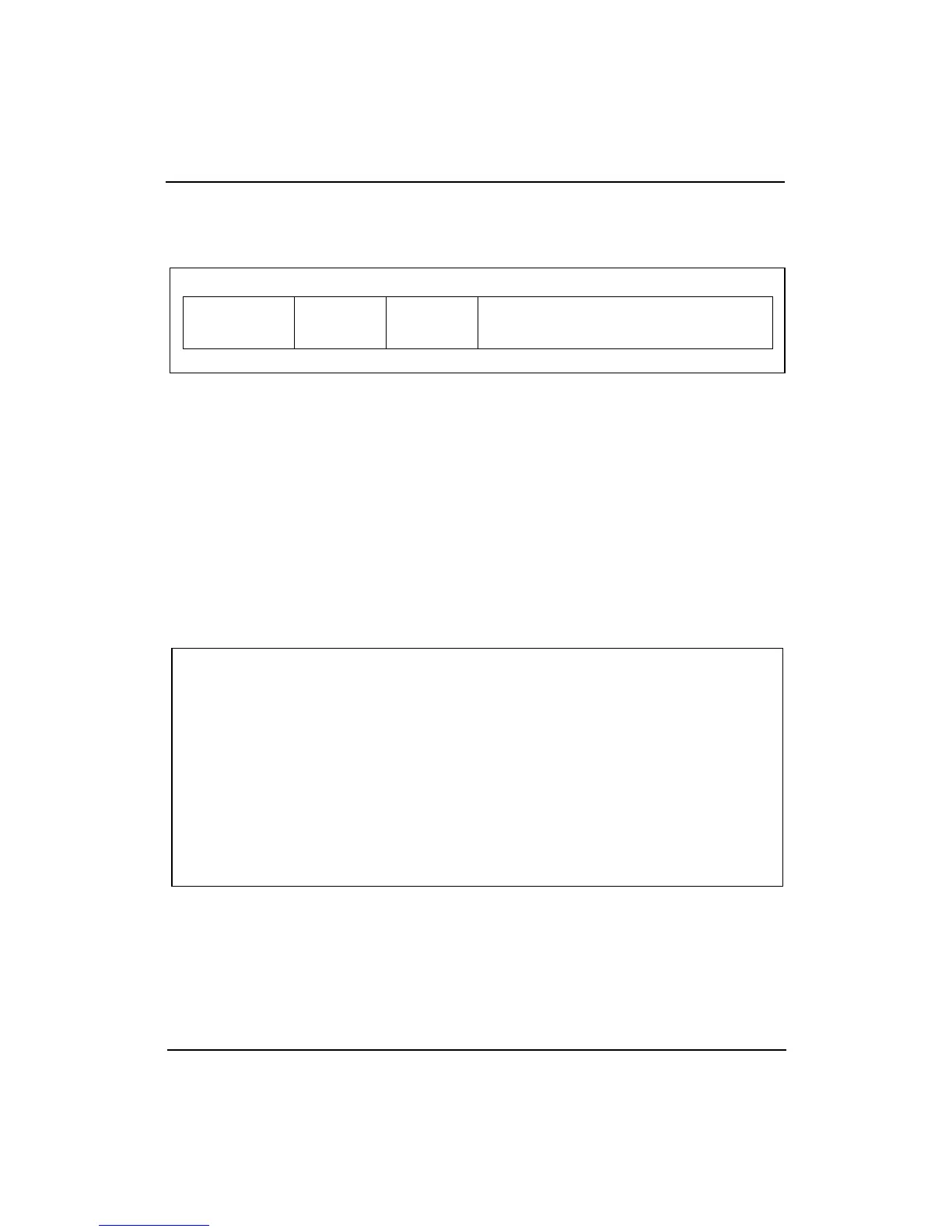

Format:

BGTZ rs, offset

Description:

A branch target address is computed from the sum of the address of the

instruction in the delay slot and the 16-bit offset, shifted left two bits and

sign-extended. The contents of general register rs are compared to zero. If

the contents of general register rs have the sign bit cleared and are not

equal to zero, then the program branches to the target address, with a

delay of one instruction.

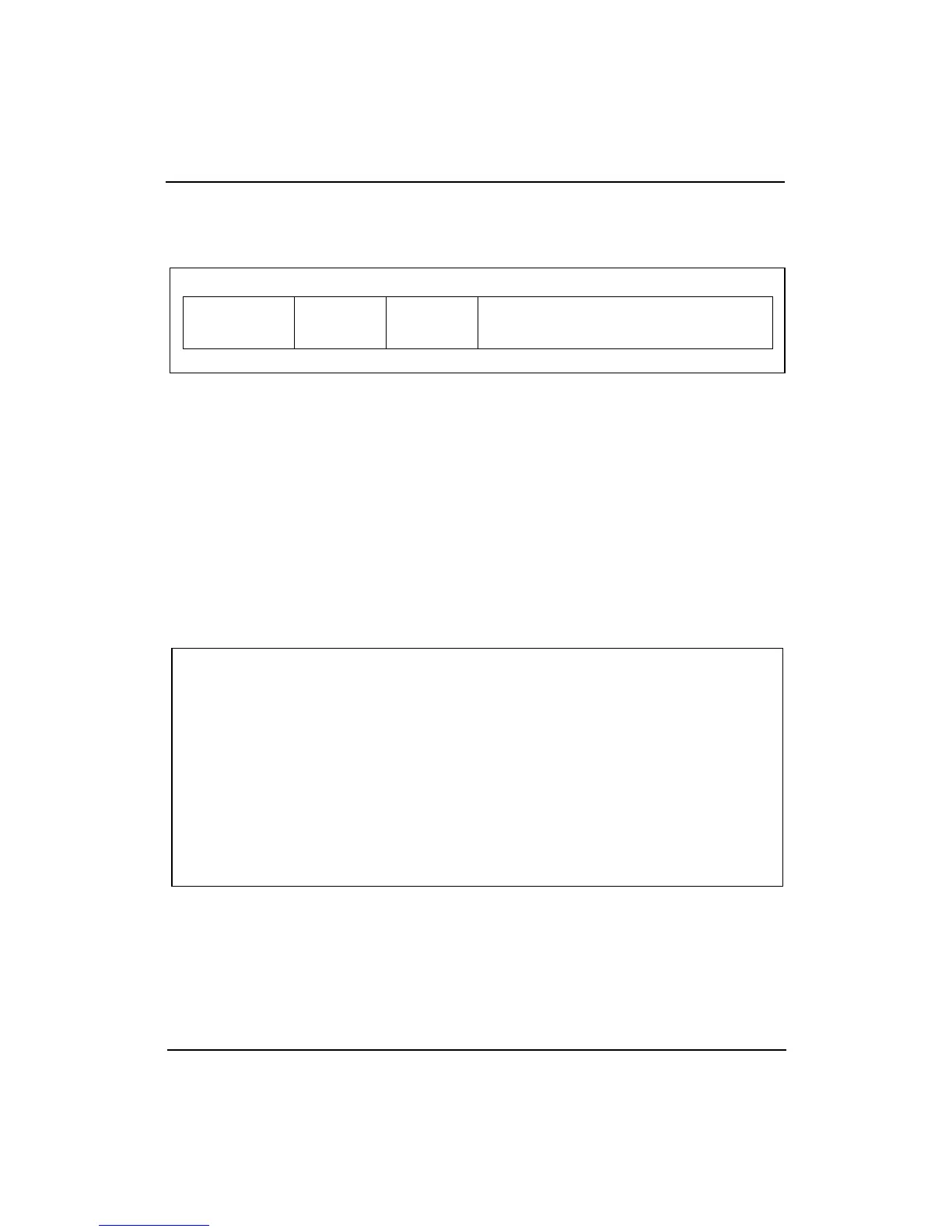

Operation:

Exceptions:

None

BGTZ

Branch On Greater Than Zero

31 2526 2021 1516 0

BGTZ rs 0

offset

655 16

0 0 0 1 1 1 0 0 0 0 0

BGTZ

32 T: target ← (offset

15

)

14

|| offset || 0

2

condition ← (GPR[rs]

31

= 0) and (GPR[rs] ≠ 0

32

)

T+1: if condition then

PC ← PC + target

endif

64 T: target ← (offset

15

)

46

|| offset || 0

2

condition ← (GPR[rs]

63

= 0) and (GPR[rs] ≠ 0

64

)

T+1: if condition then

PC ← PC + target

endif

Loading...

Loading...