MIPS R4000 Microprocessor User's Manual A-43

CPU Instruction Set Details

Write back from a primary cache goes to the secondary cache (if there is

one), otherwise to memory. Write back from a secondary cache always

goes to memory. A secondary write back always writes the most recent

data; the data comes from the primary data cache, if present, and modified

(the W bit is set). Otherwise the data comes from the specified secondary

cache. The address to be written is specified by the cache tag and not the

translated physical address.

TLB Refill and TLB Invalid exceptions can occur on any operation. For

Index operations (where the physical address is used to index the cache

but need not match the cache tag) unmapped addresses may be used to

avoid TLB exceptions. This operation never causes TLB Modified or

Virtual Coherency exceptions.

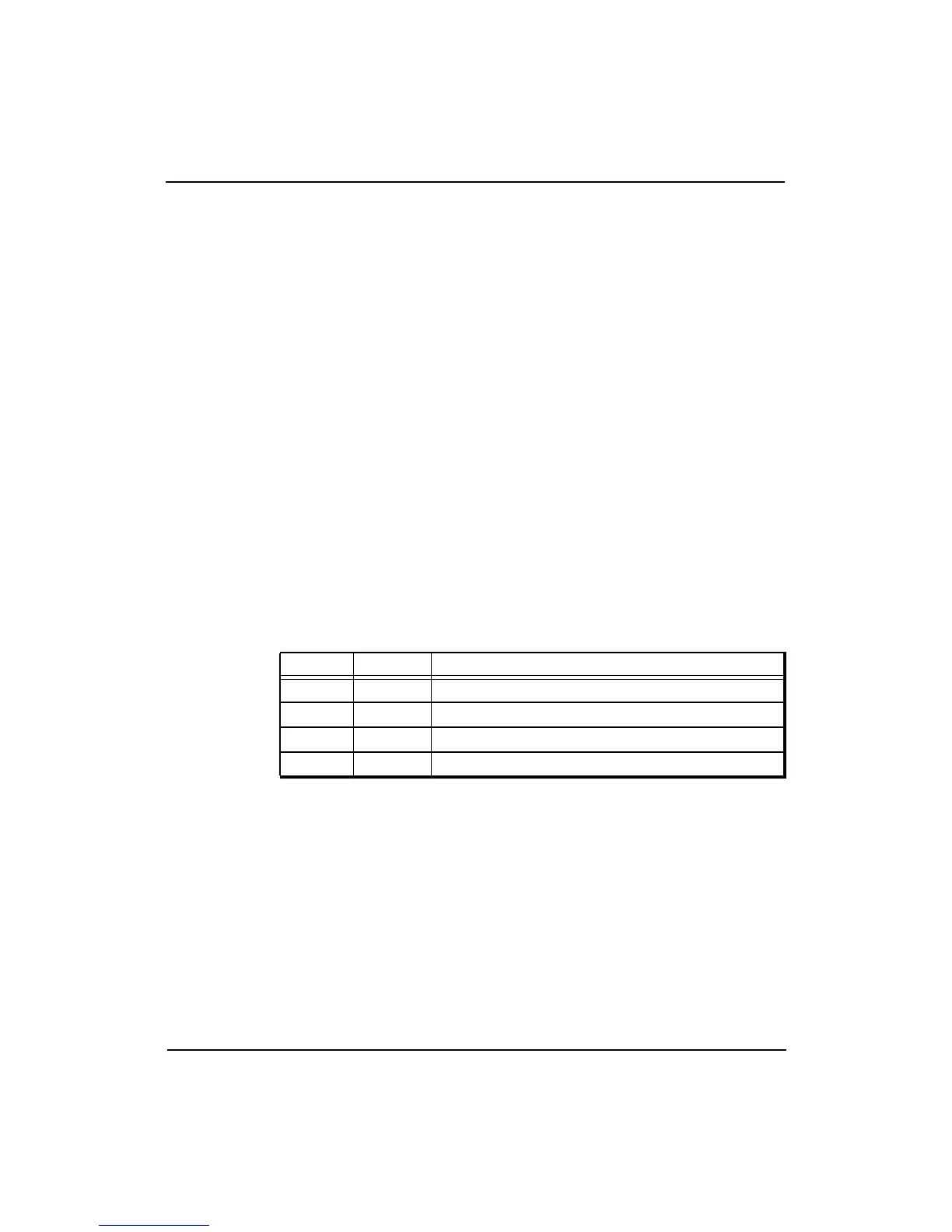

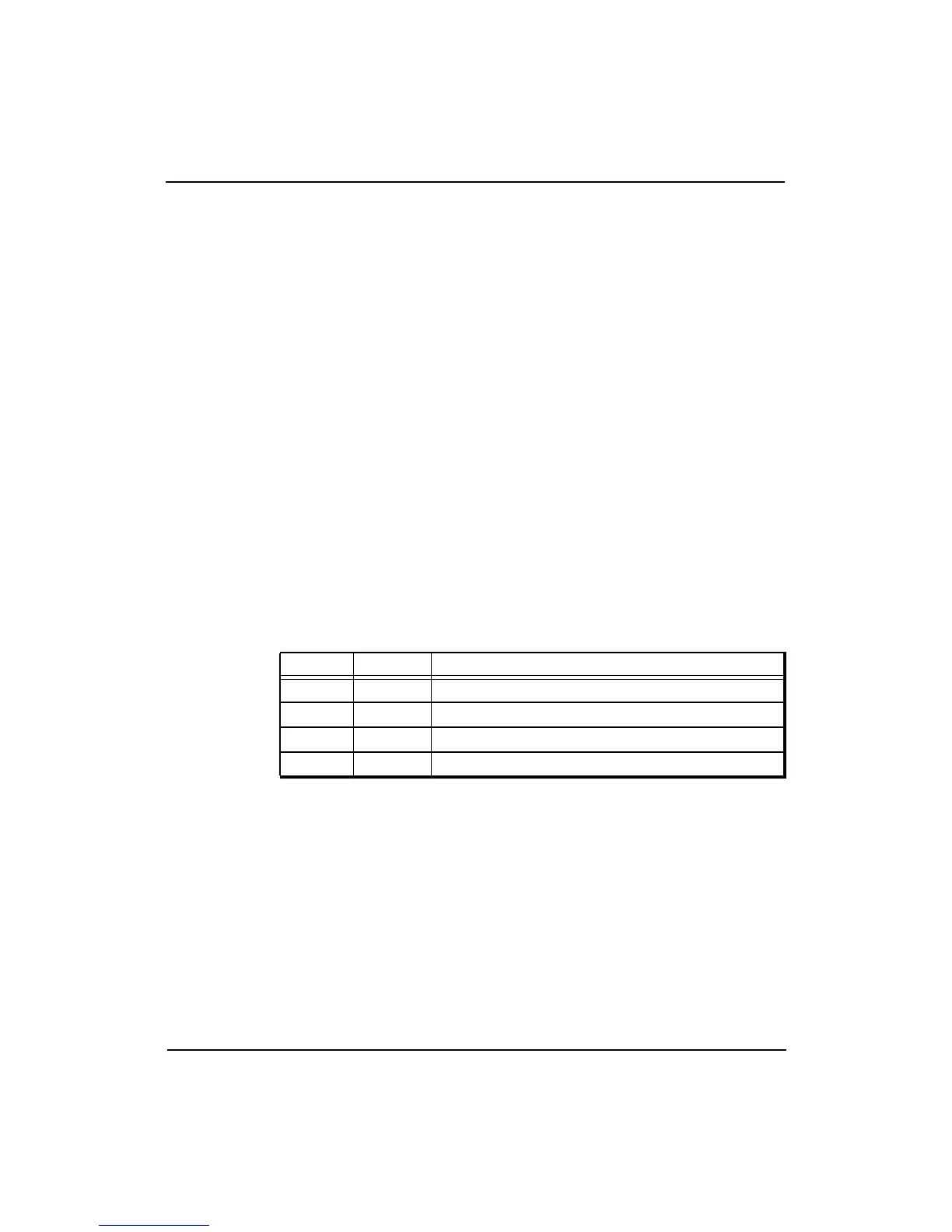

Bits 17...16 of the instruction specify the cache as follows:

Code Name Cache

0 I primary instruction

1 D primary data

2 SI secondary instruction

3 SD secondary data (or combined instruction/data)

(continued)

CACHE

ac

e

CACHE

Loading...

Loading...