MIPS R4000 Microprocessor User's Manual A-45

CPU Instruction Set Details

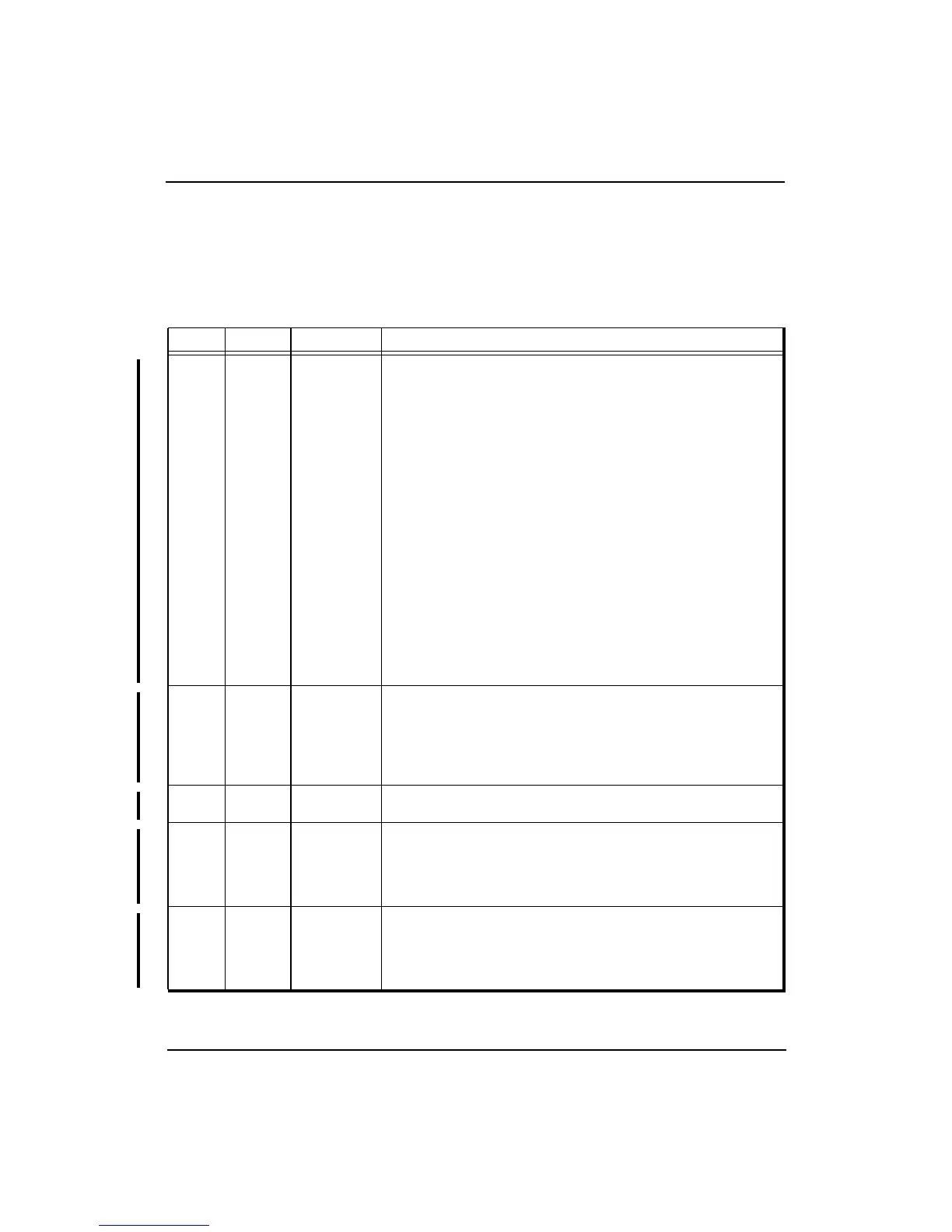

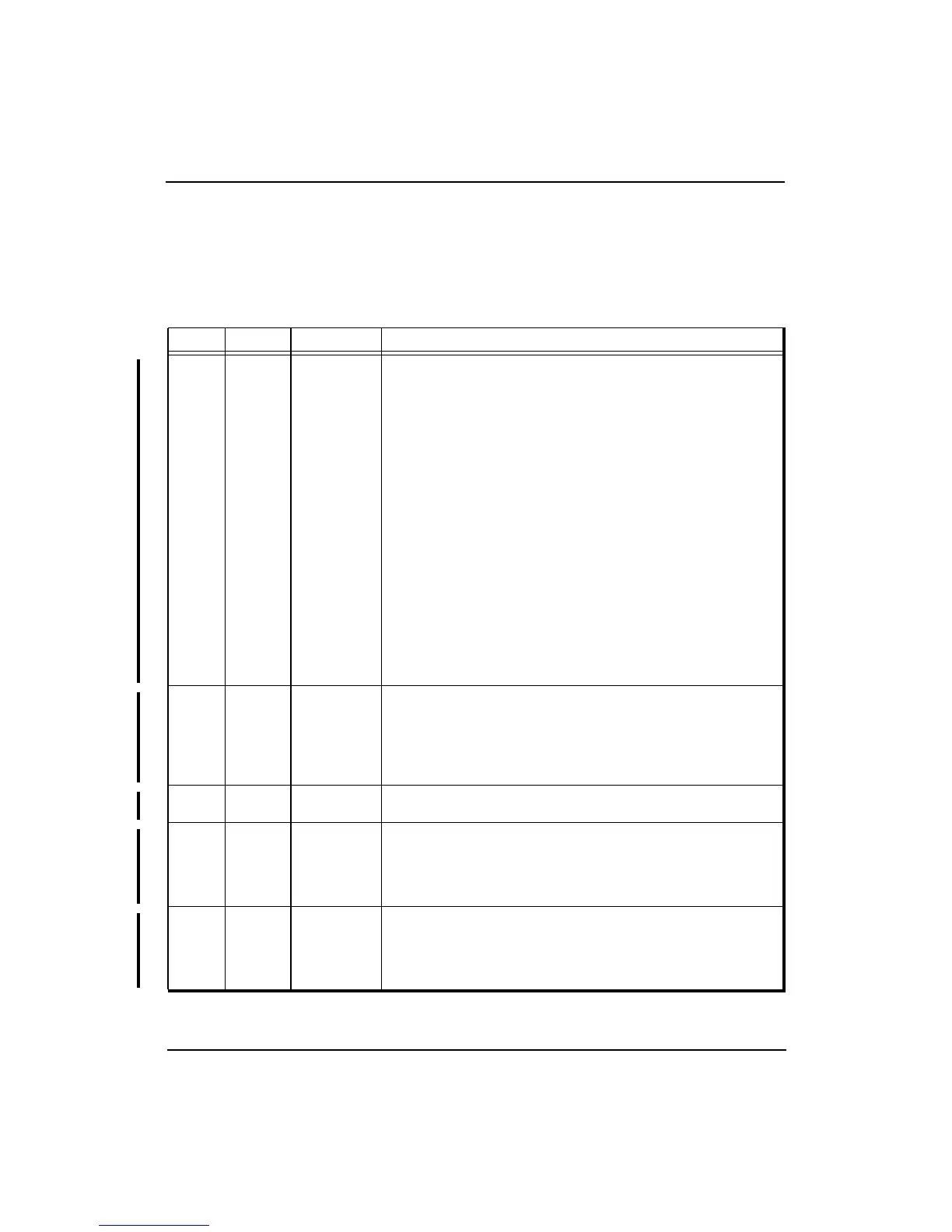

Code Caches Name Operation

3SD

Create Dirty

Exclusive

This operation is used to avoid loading data needlessly from memory

when writing new contents into an entire cache block. If the cache block

is valid but does not contain the specified address (a valid miss) the

secondary block is vacated. The data is written back to memory if dirty

and all matching blocks in both primary caches are invalidated. As usual

during a secondary writeback, if the primary data cache contains

modified data (matching blocks with

W

bit set) that modified data is

written to memory. If the cache block is valid and contains the specified

physical address (a hit), the operation cleans up the primary caches to

avoid virtual aliases: all blocks in both primary caches that match the

secondary line are invalidated without writeback. Note that the search for

matching primary blocks uses the virtual index of the

PIdx

field of the

secondary cache tag (the virtual index when the location was last used)

and not the virtual index of the virtual address used in the operation (the

virtual index where the location will now be used). If the secondary tag

and address do not match (miss), or the tag and address do match (hit)

and the block is in a shared state, an invalidate for the specified address

is sent over the System interface. In all cases, the cache block tag must

be set to the specified physical address, the cache state must be set to

Dirty Exclusive, and the virtual index field set from the virtual address.

The

CH

bit in the

Status

register is set or cleared to indicate a hit or miss.

3D

Create Dirty

Exclusive

This operation is used to avoid loading data needlessly from secondary

cache or memory when writing new contents into an entire cache block.

If the cache block does not contain the specified address, and the block

is dirty, write it back to the secondary cache (if present) or otherwise to

memory. In all cases, set the cache block tag to the specified physical

address, set the cache state to Dirty Exclusive.

4 I,D Hit Invalidate

If the cache block contains the specified address, mark the cache block

invalid.

4 SI, SD Hit Invalidate

If the cache block contains the specified address, mark the cache block

invalid and also invalidate all matching blocks, if present, in the primary

caches (the

PIdx

field of the secondary tag is used to determine the

locations in the primaries to search). The

CH

bit in the

Status

register is

set or cleared to indicate a hit or miss.

5D

Hit Writeback

Invalidate

If the cache block contains the specified address, write the data back if it

is dirty, and mark the cache block invalid. When a secondary cache is

present, and the

CE

bit of the

Status

register is set, the contents of the

ECC

register is XOR’d into the computed check bits during the write to

the secondary cache for the addressed doubleword.

CACHE

CACHE

(continued)

ache

Loading...

Loading...