MIPS R4000 Microprocessor User's Manual A-61

CPU Instruction Set Details

Format:

DMFC0 rt, rd

Description:

The contents of coprocessor register rd of the CP0 are loaded into general

register rt.

This operation is defined for the R4000 operating in 64-bit mode and in 32-

bit kernel mode. Execution of this instruction in 32-bit user or supervisor

mode causes a reserved instruction exception. All 64-bits of the general

register destination are written from the coprocessor register source. The

operation of DMFC0 on a 32-bit coprocessor 0 register is undefined.

Operation:

Exceptions:

Coprocessor unusable exception

Reserved instruction exception (R4000 in 32-bit user mode

R4000 in 32-bit supervisor mode)

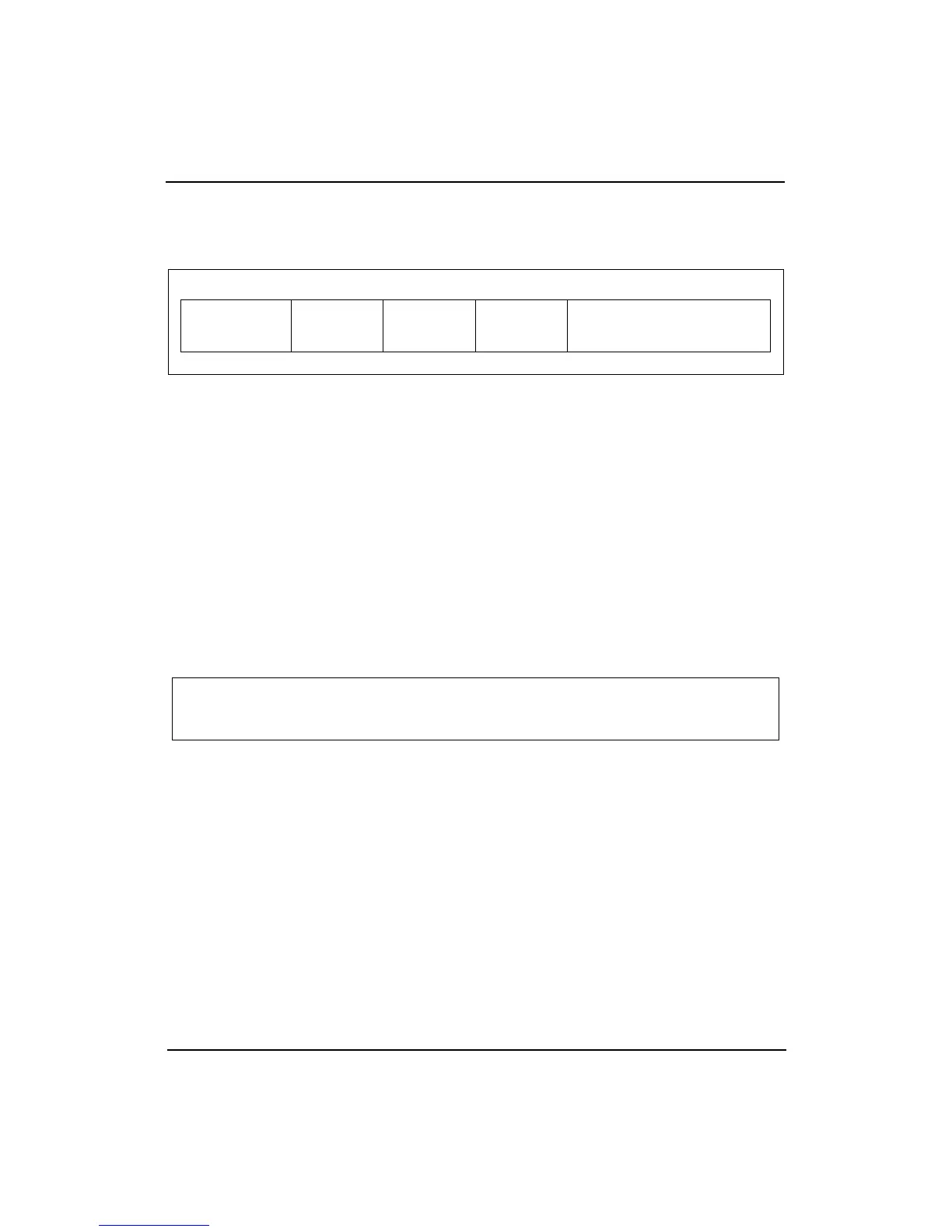

DMFC0

Doubleword Move From

rd

11 10

5

31 2526 2021 1516 0

COP0 DMF rt

0

655 11

System Control Coprocessor

0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 00

DMFC0

64 T: data ←CPR[0,rd]

T+1: GPR[rt] ← data

Loading...

Loading...