Appendix A

A-62 MIPS R4000 Microprocessor User's Manual

Format:

DMTC0 rt, rd

Description:

The contents of general register rt are loaded into coprocessor register rd

of the CP0.

This operation is defined for the R4000 operating in 64-bit mode or in 32-

bit kernel mode. Execution of this instruction in 32-bit user or supervisor

mode causes a reserved instruction exception.

All 64-bits of the coprocessor 0 register are written from the general

register source. The operation of DMTC0 on a 32-bit coprocessor 0 register

is undefined.

Because the state of the virtual address translation system may be altered

by this instruction, the operation of load instructions, store instructions,

and TLB operations immediately prior to and after this instruction are

undefined.

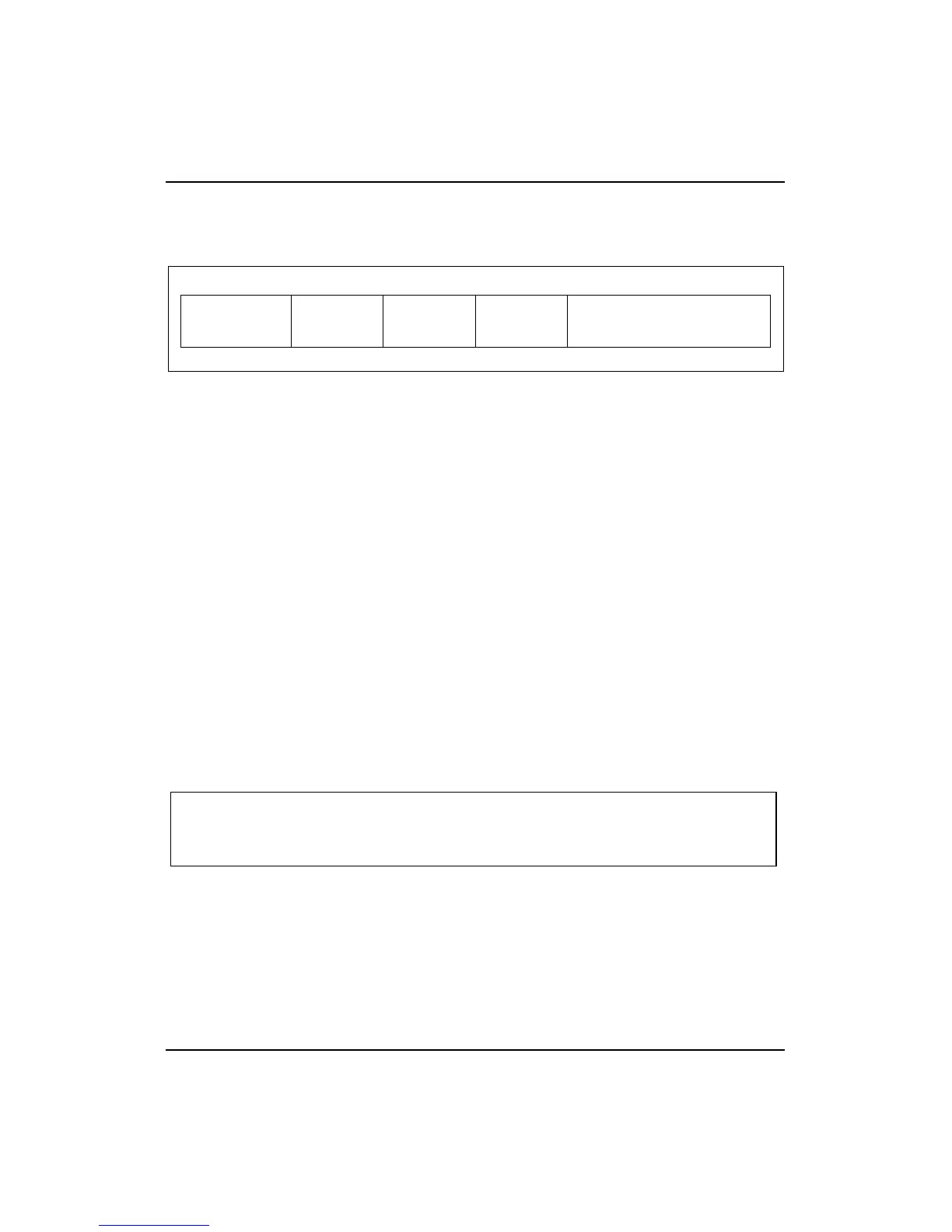

Operation:

Exceptions:

Coprocessor unusable exception (R4000 in 32-bit user mode

R4000 in 32-bit supervisor mode)

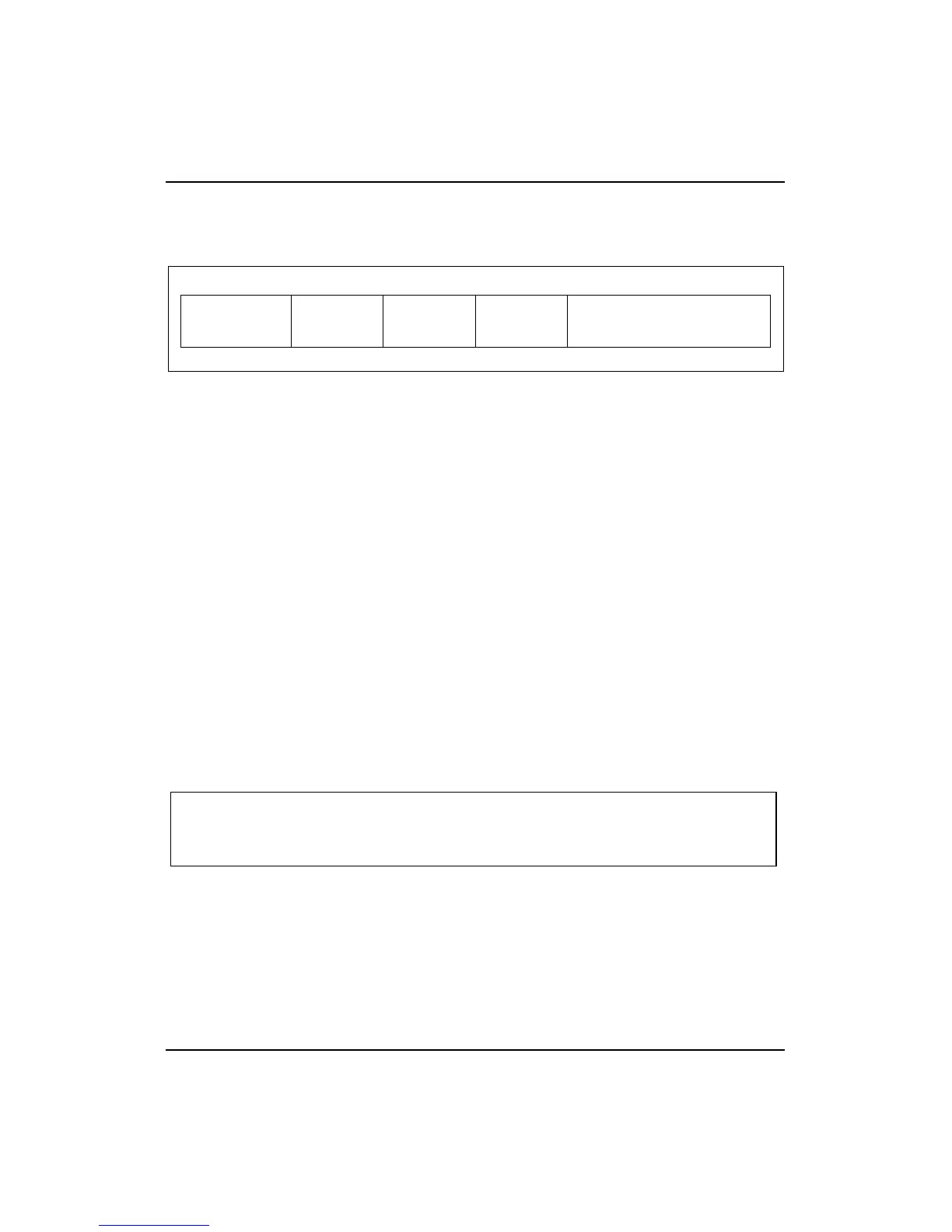

DMTC0

Doubleword Move To

rd

11 10

5

31 2526 2021 1516 0

COP0 DMT rt

0

655 11

System Control Coprocessor

0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 00

DMTC0

64 T: data ← GPR[rt]

T+1: CPR[0,rd] ← data

Loading...

Loading...