Appendix A

A-76 MIPS R4000 Microprocessor User's Manual

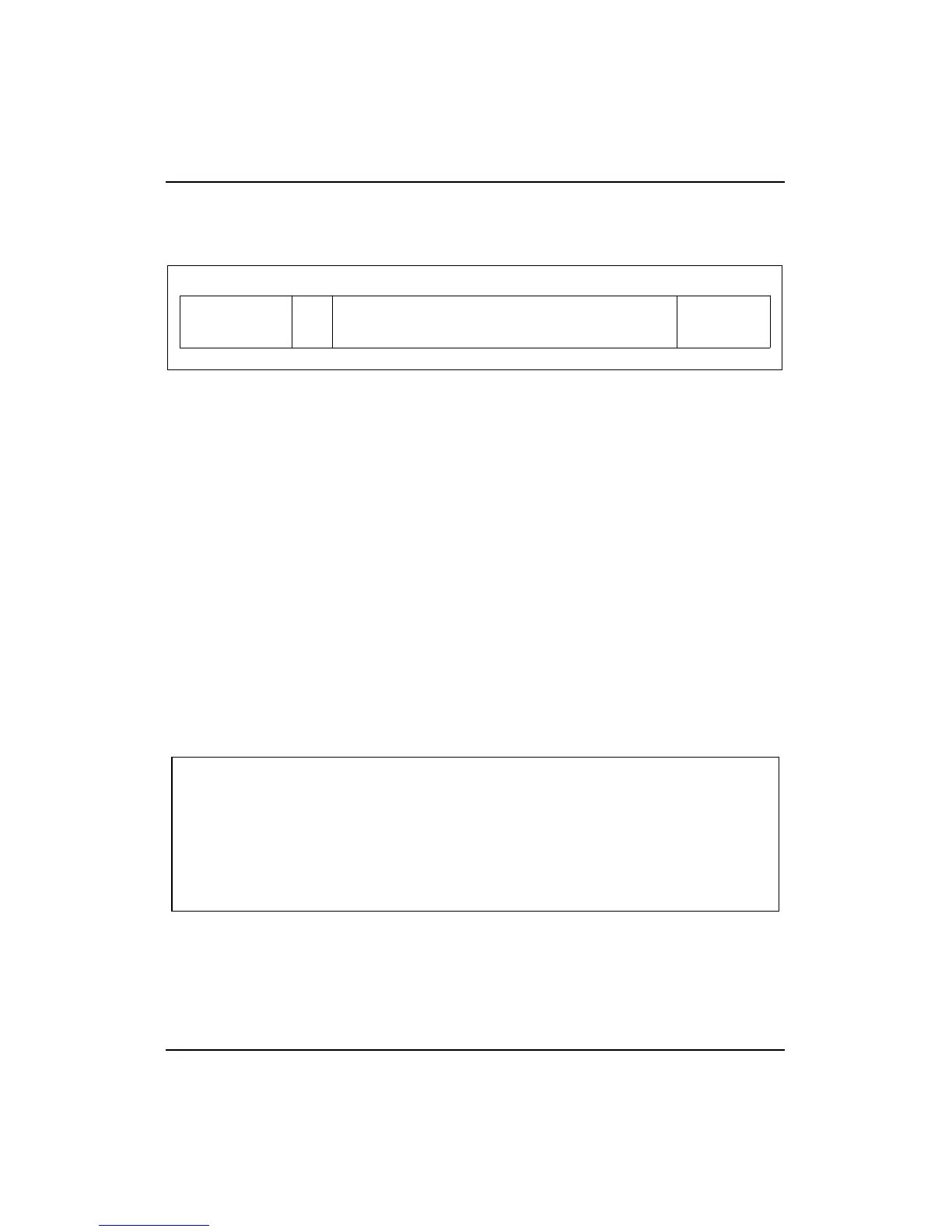

Format:

ERET

Description:

ERET is the R4000 instruction for returning from an interrupt, exception,

or error trap. Unlike a branch or jump instruction, ERET does not execute

the next instruction.

ERET must not itself be placed in a branch delay slot.

If the processor is servicing an error trap (SR

2

= 1), then load the PC from

the ErrorEPC and clear the ERL bit of the Status register (SR

2

). Otherwise

(SR

2

= 0), load the PC from the EPC, and clear the EXL bit of the Status

register (SR

1

).

An ERET executed between a LL and SC also causes the SC to fail.

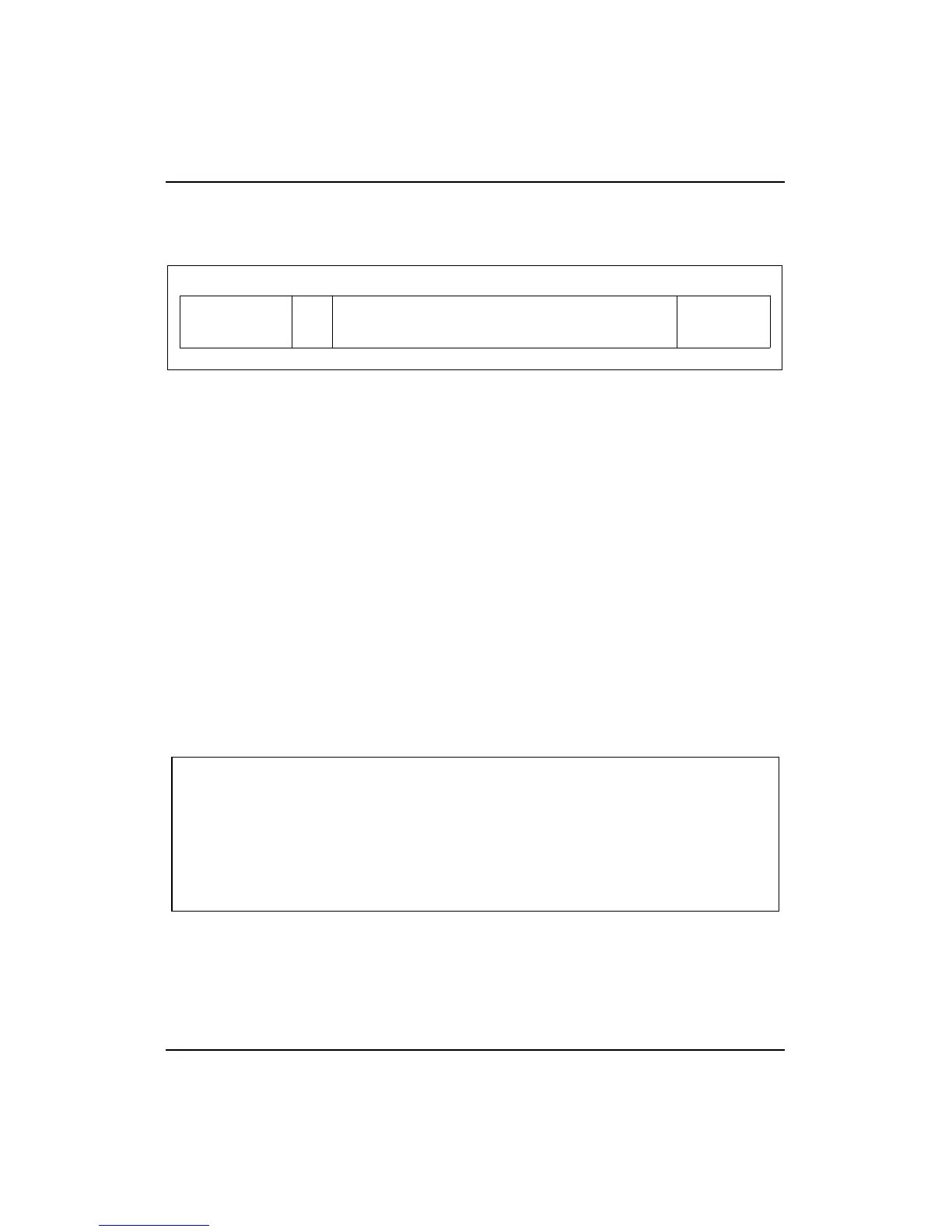

Operation:

Exceptions:

Coprocessor unusable exception

ERET

Exception Return

0

6

6 531 25 2426

COP0

6

0

ERET

191

CO

0 1 0 0 0 0 0 1 1 0 0 01 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

ERET

32, 64 T: if SR

2

= 1 then

PC ← ErrorEPC

SR ← SR

31...3

|| 0 || SR

1...0

else

PC ← EPC

SR ← SR

31...2

|| 0 || SR

0

endif

LLbit ← 0

Loading...

Loading...