Appendix A

A-84 MIPS R4000 Microprocessor User's Manual

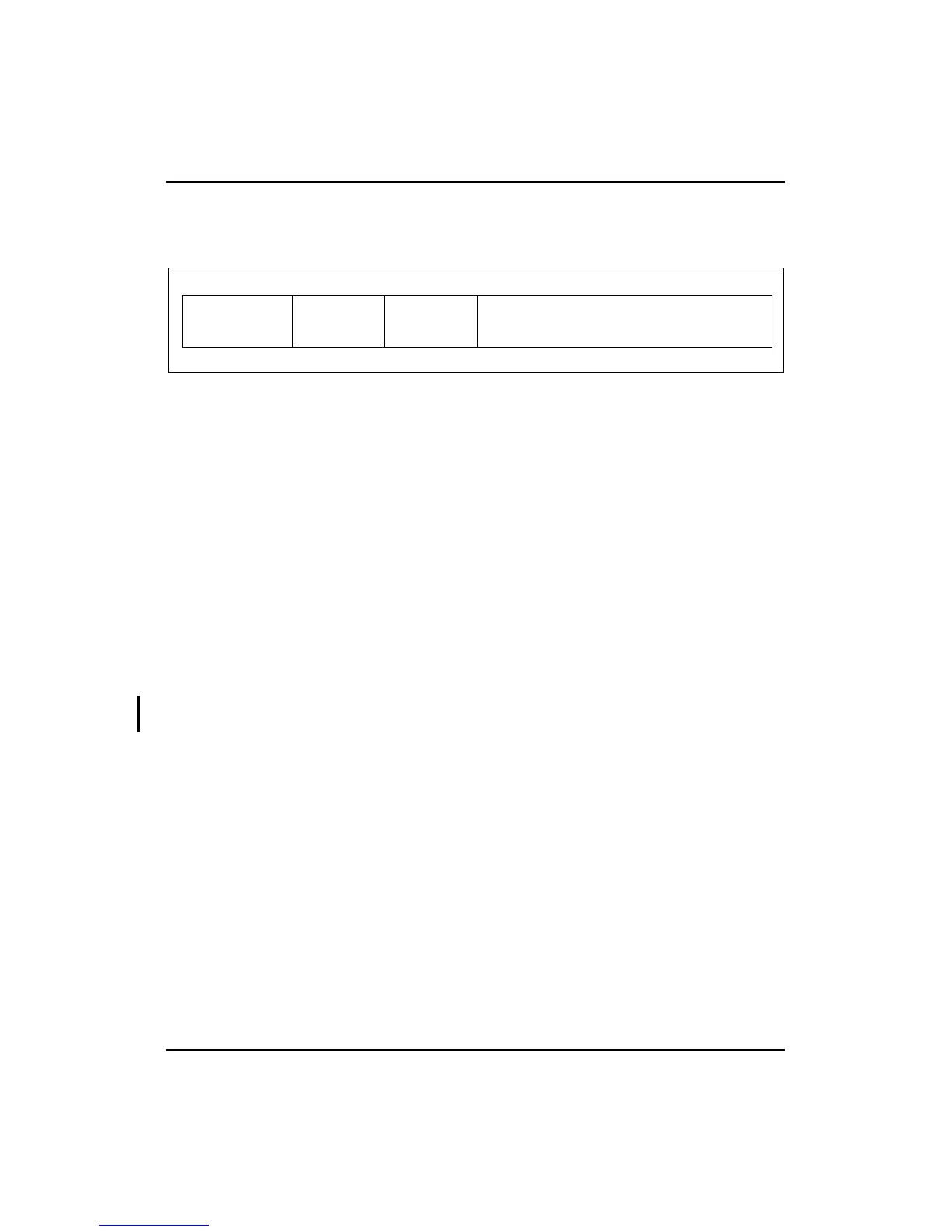

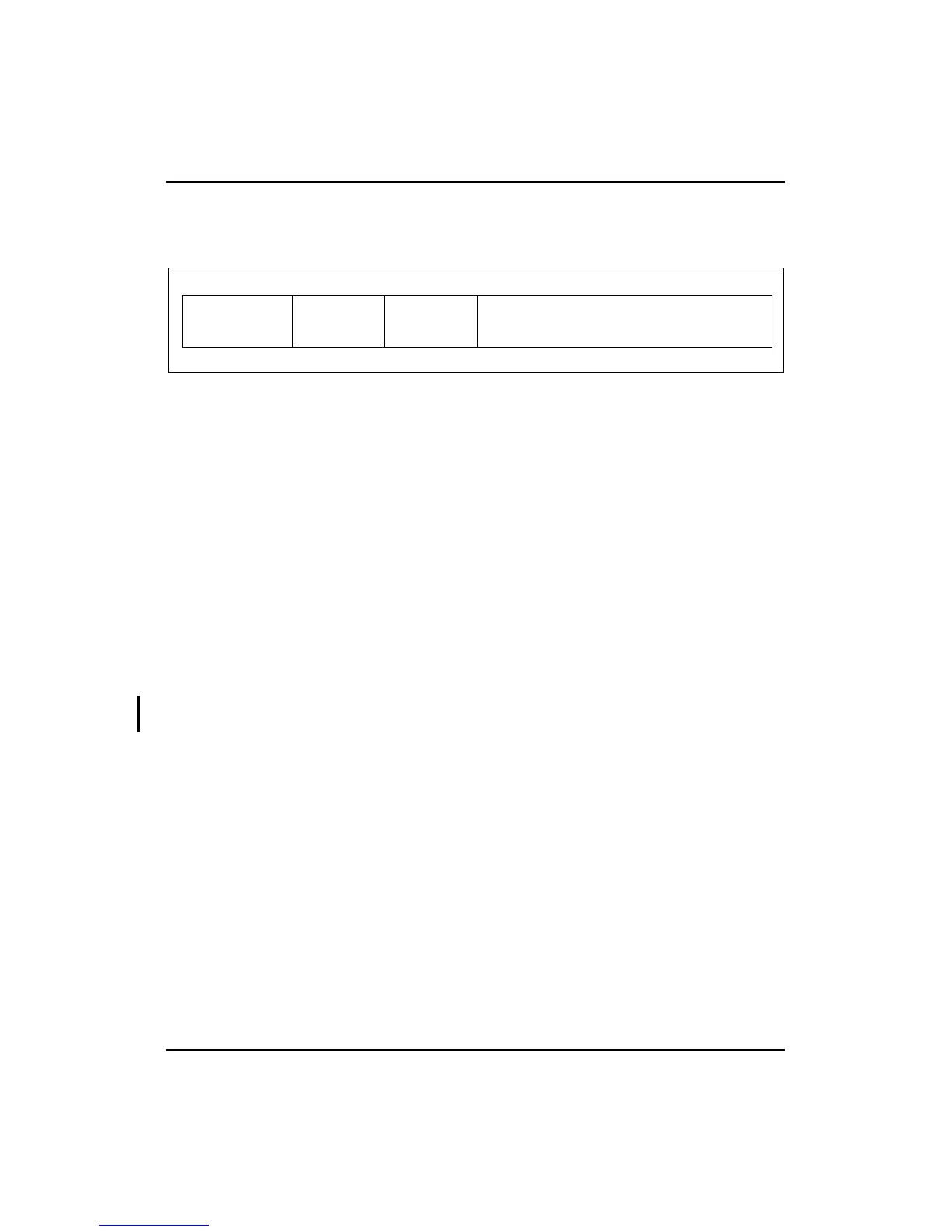

Format:

LDCz rt, offset(base)

Description:

The 16-bit offset is sign-extended and added to the contents of general

register base to form a virtual address. The processor reads a doubleword

from the addressed memory location and makes the data available to

coprocessor unit z. The manner in which each coprocessor uses the data

is defined by the individual coprocessor specifications.

If any of the three least-significant bits of the effective address are non-

zero, an address error exception takes place.

This instruction is not valid for use with CP0.

This instruction is undefined when the least-significant bit of the

rt field is non-zero.

*See the table “Opcode Bit Encoding” on next page, or “CPU Instruction

Opcode Bit Encoding” at the end of Appendix A.

LDCz

Load Doubleword To Coprocessor

31 2526 2021 1516 0

LDCz base rt

offset

655 16

1 1 0 1 x x*

LDCz

Loading...

Loading...