Appendix A

A-98 MIPS R4000 Microprocessor User's Manual

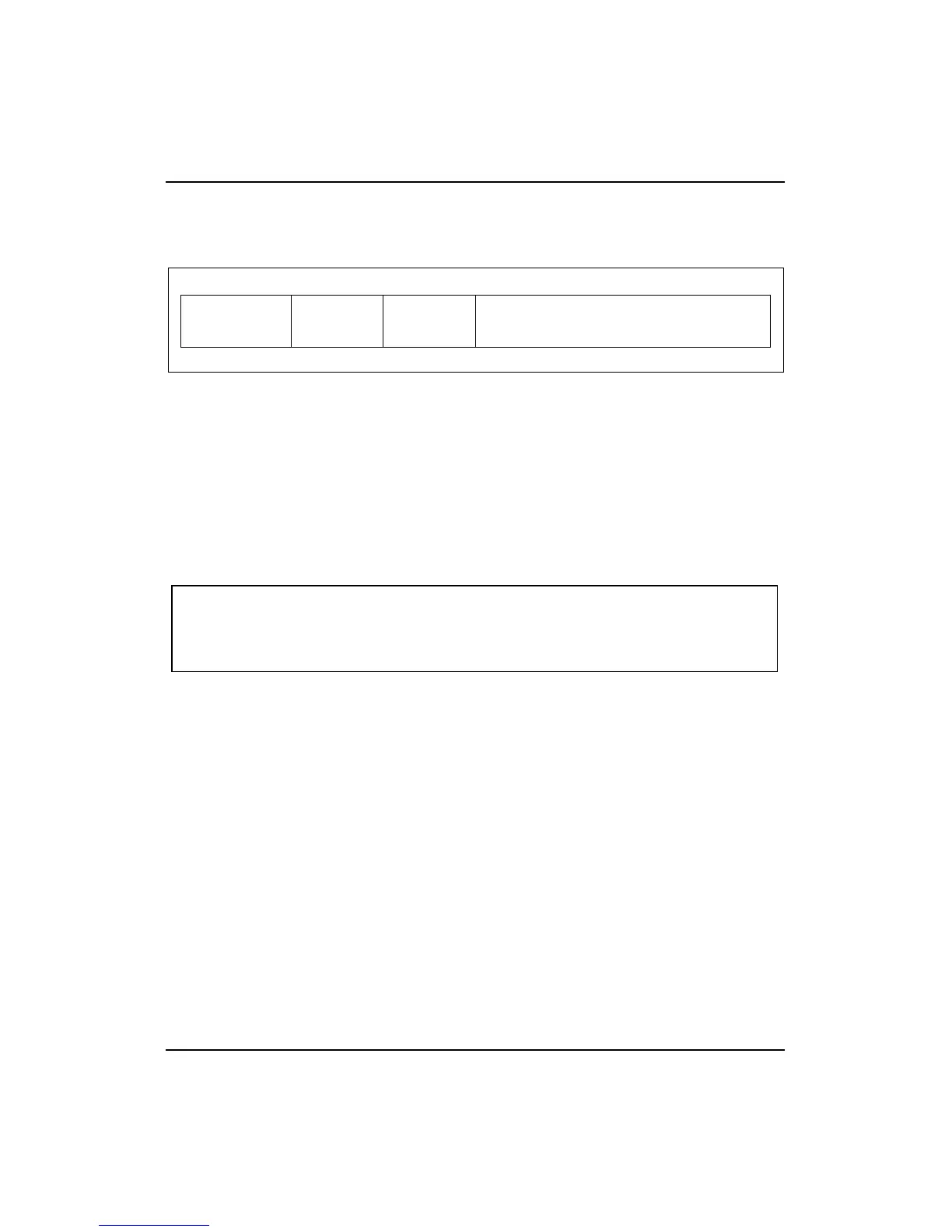

Format:

LUI rt, immediate

Description:

The 16-bit immediate is shifted left 16 bits and concatenated to 16 bits of

zeros. The result is placed into general register rt. In 64-bit mode, the

loaded word is sign-extended.

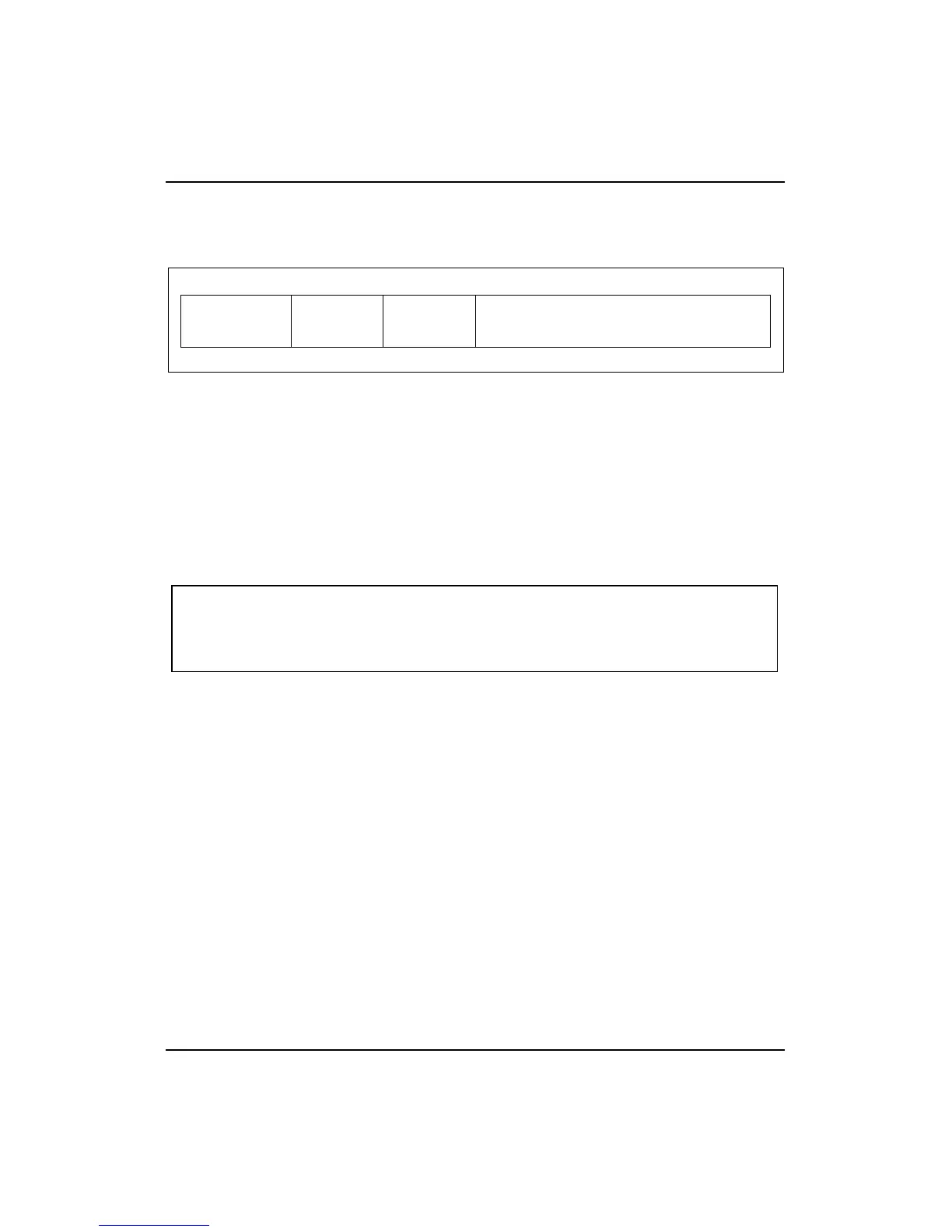

Operation:

Exceptions:

None

LUI

Load Upper Immediate

31 2526 2021 1516 0

LUI rt

immediate

655 16

0 0 1 1 1 1

LUI

0

0 0 0 0 0

32 T: GPR[rt] ← immediate || 0

16

64 T: GPR[rt] ← (immediate

15

)

32

|| immediate || 0

16

Loading...

Loading...