Appendix A

A-104 MIPS R4000 Microprocessor User's Manual

Given a doubleword in a register and a doubleword in memory, the

operation of LWL is as follows:

LEM Little-endian memory (BigEndianMem = 0)

BEM BigEndianMem = 1

Type AccessType (see Table 2-1) sent to memory

Offset pAddr

2...0

sent to memory

S sign-extend of destination

31

Exceptions:

TLB refill exception

TLB invalid exception

Bus error exception

Address error exception

LWL

LWL

(continued)

Load Word Left

LWL

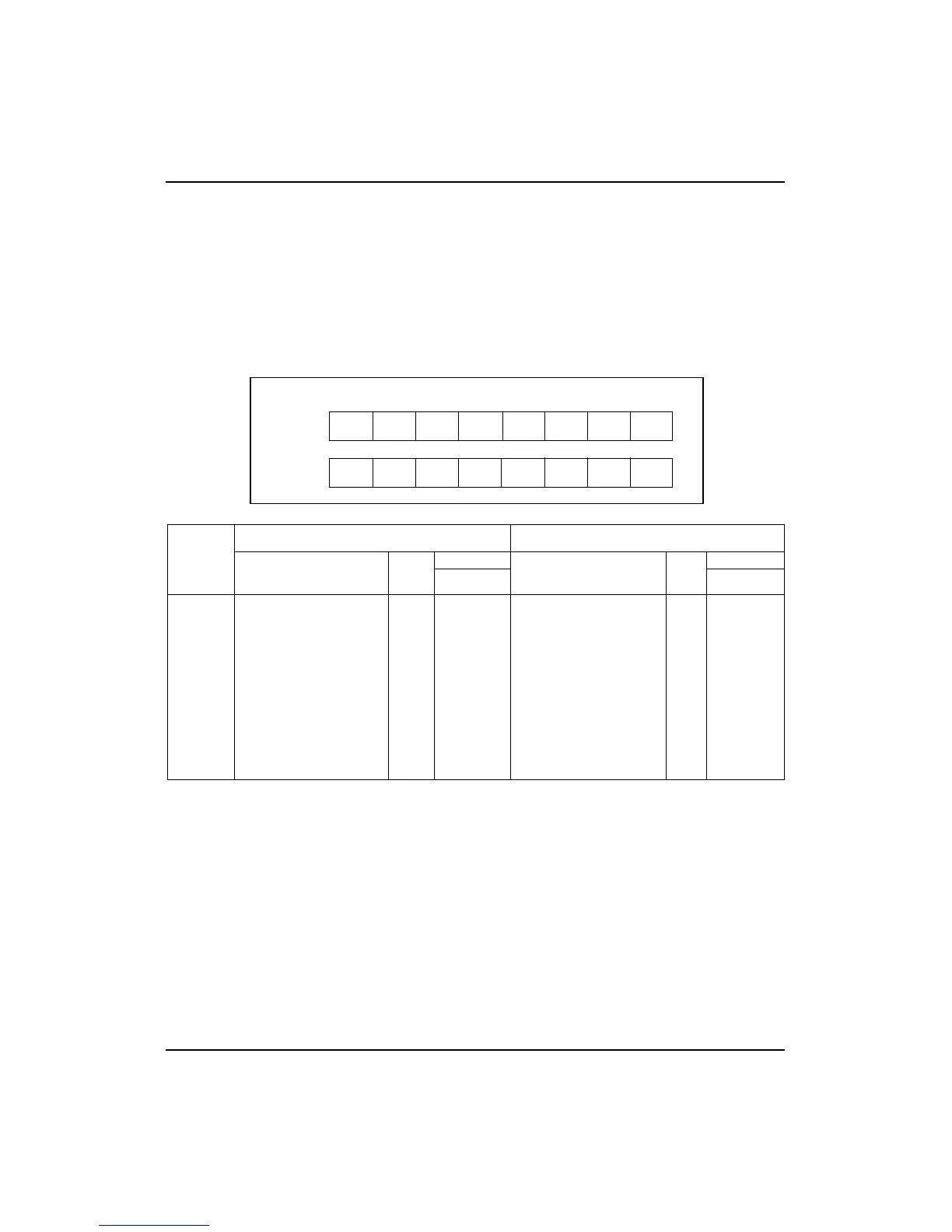

ACDB

Register

IKLJ

Memory

EGHF

MOPN

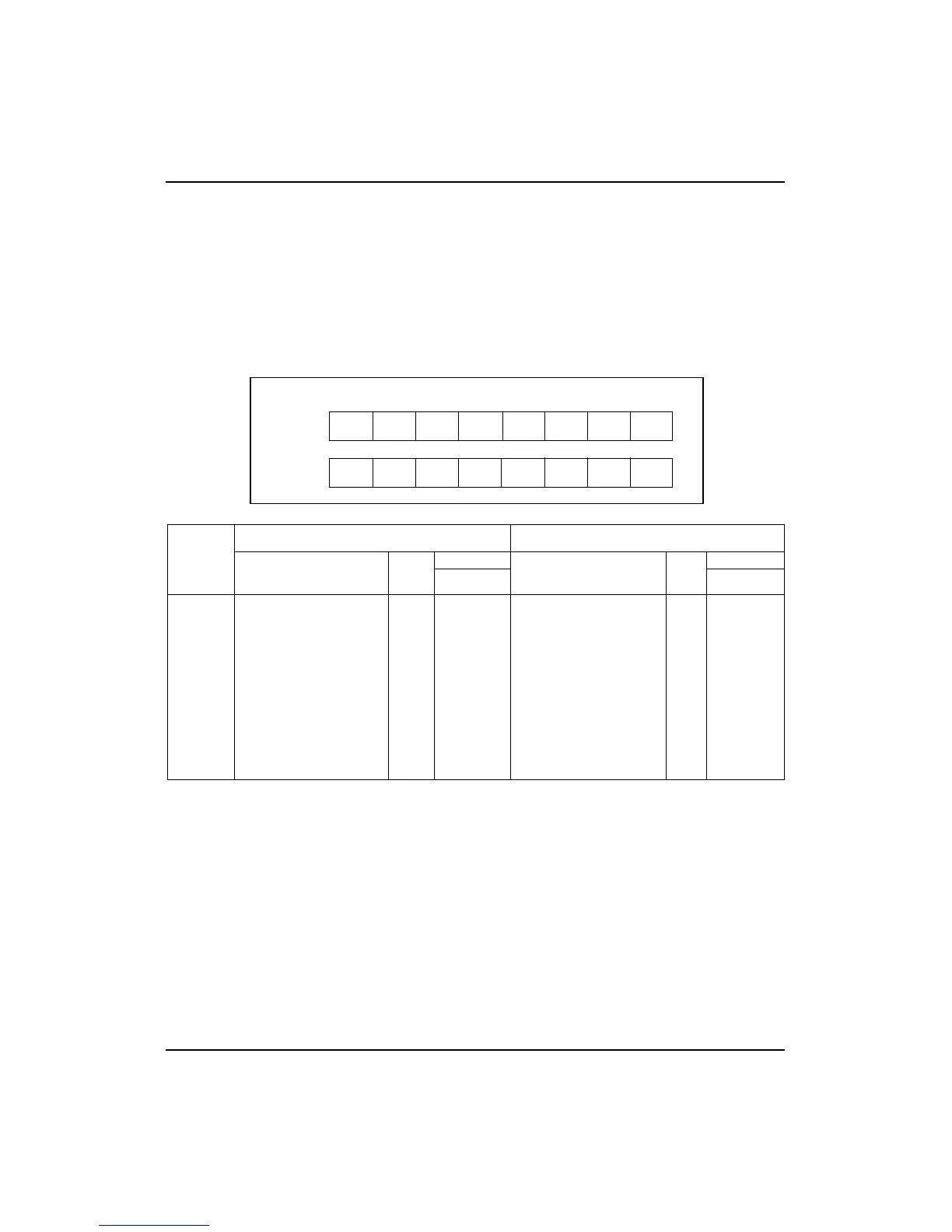

0SSSSPFGH007SSSSIJKL340

1SSSSOPGH106SSSSJKLH241

2SSSSNOPH205SSSSKLGH142

3SSSSMNOP304SSSSLFGH043

4SSSSLFGH043SSSSMNOP304

5SSSSKLGH142SSSSNOPH205

6SSSSJKLH241SSSSOPGH106

7SSSSIJKL340SSSSPFGH007

BigEndianCPU = 0

vAddr

2..0

destination

destination

type

type

offset

offset

BigEndianCPU = 1

LEM BEM

LEM BEM

Loading...

Loading...