MIPS R4000 Microprocessor User's Manual A-113

CPU Instruction Set Details

Format:

MFLO rd

Description:

The contents of special register LO are loaded into general register rd.

To ensure proper operation in the event of interruptions, the two

instructions which follow a MFLO instruction may not be any of the

instructions which modify the LO register: MULT, MULTU, DIV, DIVU,

MTLO, DMULT, DMULTU, DDIV, DDIVU.

Operation:

Exceptions:

None

MFLO

Move From Lo

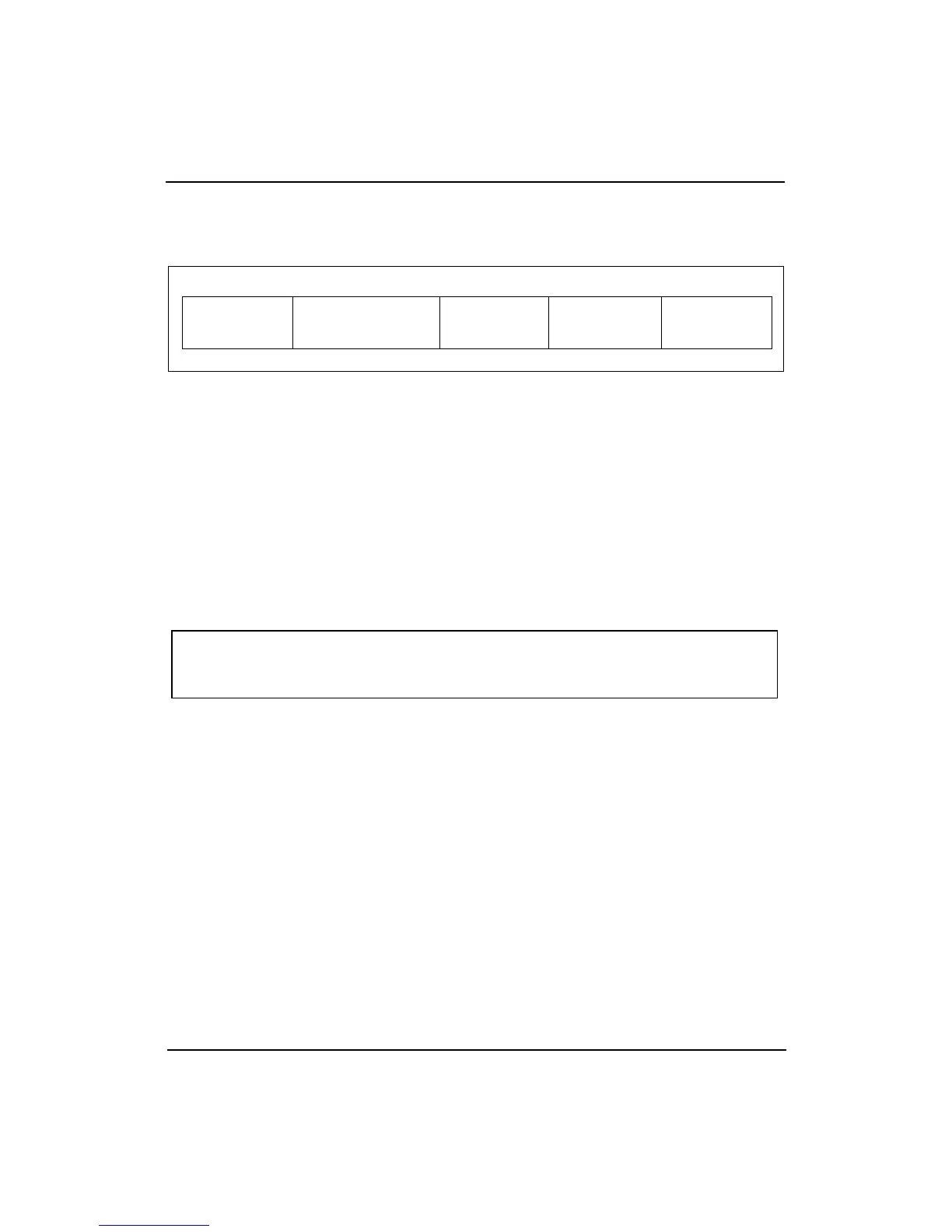

0

31 2526 1516 0

rd

6105

65

6

SPECIAL MFLO0

5

11 10

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0

MFLO

32, 64 T: GPR[rd] ← LO

Loading...

Loading...