MIPS R4000 Microprocessor User's Manual A-117

CPU Instruction Set Details

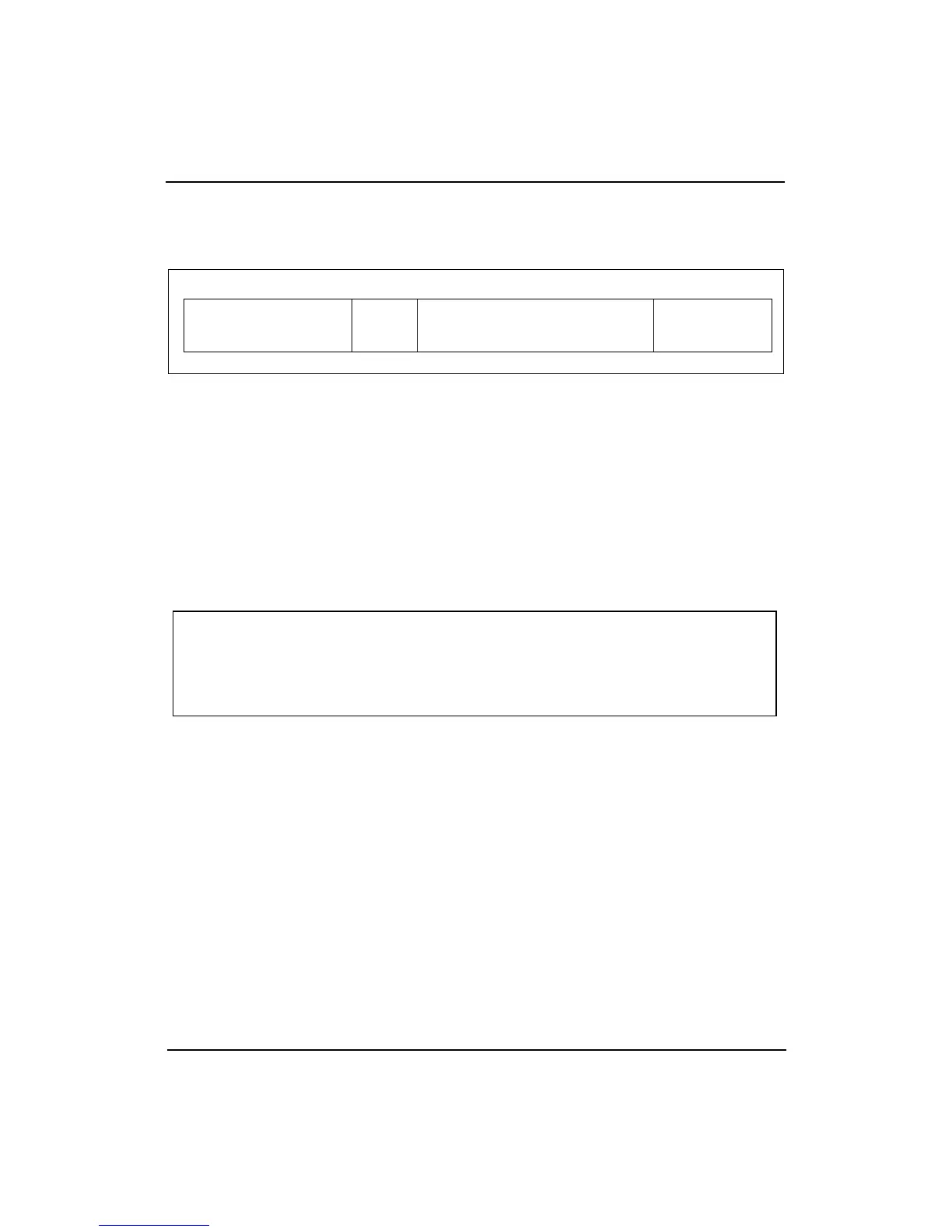

Format:

MTLO rs

Description:

The contents of general register rs are loaded into special register LO.

If a MTLO operation is executed following a MULT, MULTU, DIV, or

DIVU instruction, but before any MFLO, MFHI, MTLO, or MTHI

instructions, the contents of special register HI are undefined.

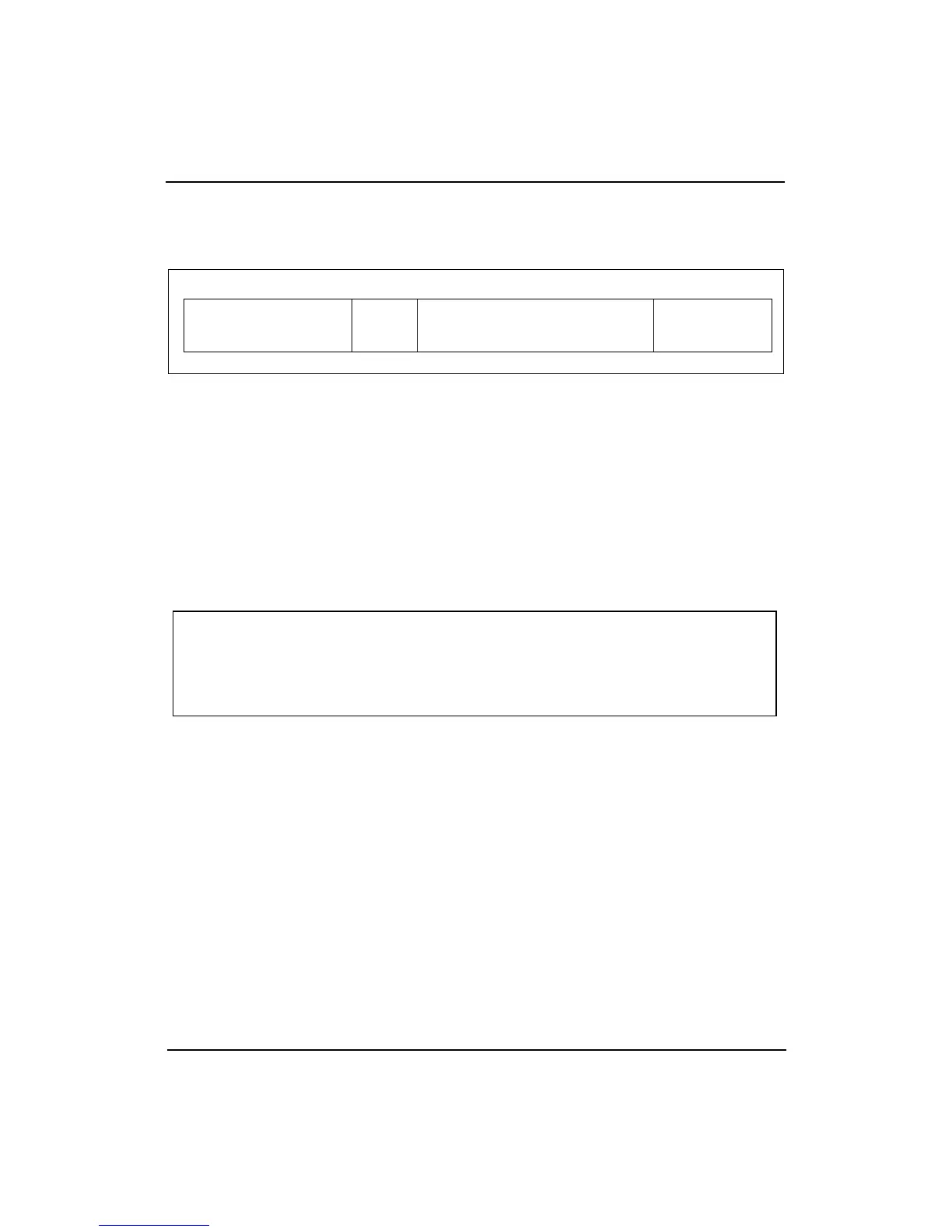

Operation:

Exceptions:

None

rs

MTLO

Move To LO

21 2031 2526

SPECIAL

6

0

MTLO0

6 5

515 6

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1

MTLO

32,64 T–2: LO ← undefined

T–1: LO ← undefined

T: LO ← GPR[rs]

Loading...

Loading...