MIPS R4000 Microprocessor User's Manual A-133

CPU Instruction Set Details

Format:

SDL rt, offset(base)

Description:

This instruction can be used with the SDR instruction to store the contents

of a register into eight consecutive bytes of memory, when the bytes cross

a doubleword boundary. SDL stores the left portion of the register into the

appropriate part of the high-order doubleword of memory; SDR stores the

right portion of the register into the appropriate part of the low-order

doubleword.

The SDL instruction adds its sign-extended 16-bit offset to the contents of

general register base to form a virtual address which may specify an

arbitrary byte. It alters only the word in memory which contains that byte.

From one to four bytes will be stored, depending on the starting byte

specified.

Conceptually, it starts at the most-significant byte of the register and

copies it to the specified byte in memory; then it copies bytes from register

to memory until it reaches the low-order byte of the word in memory.

No address exceptions due to alignment are possible.

SDL

Store Doubleword Left

31 2526 2021 1516 0

SDL base rt

offset

655 16

1 0 1 1 0 0

SDL

14

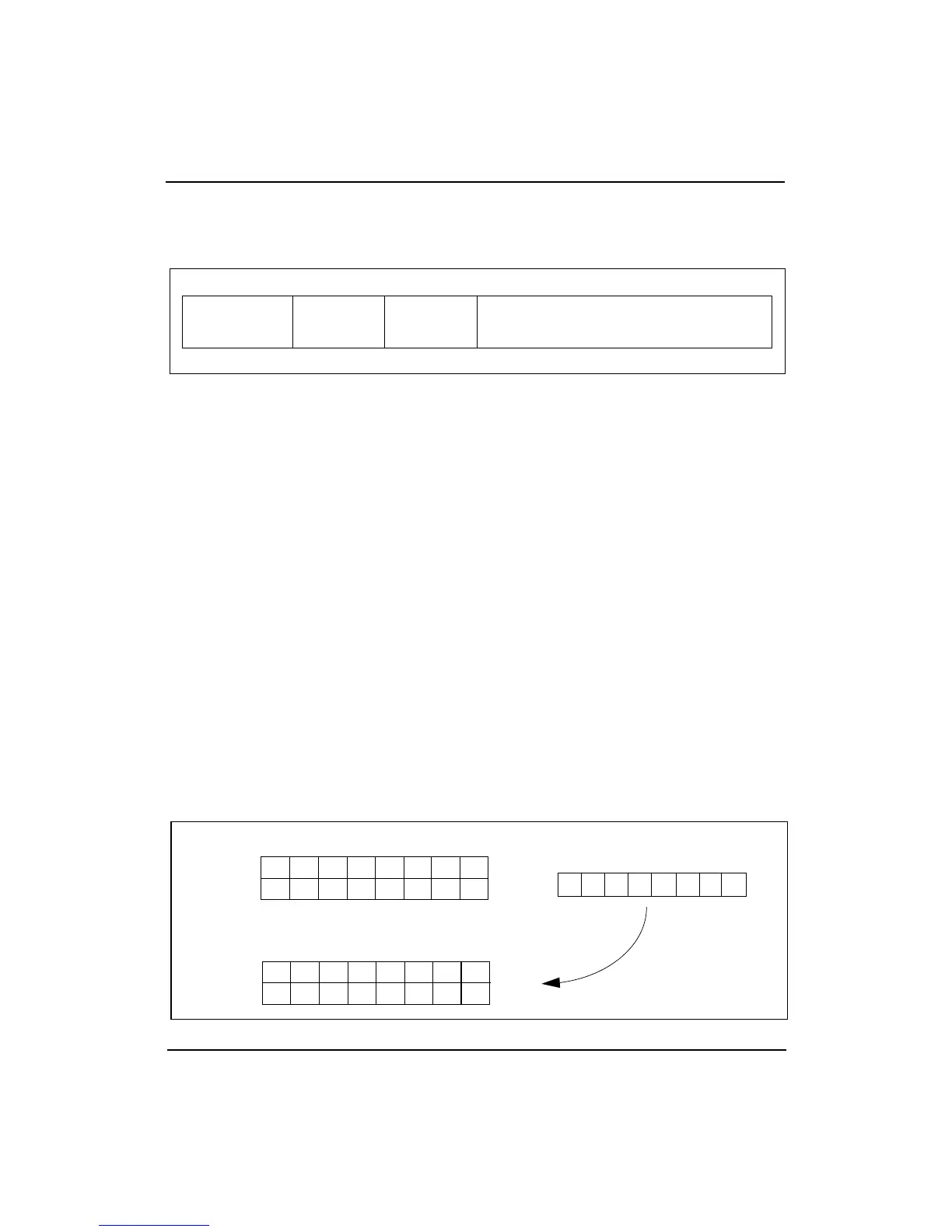

SDL $24,1($0)

after

address 0

address 8

memory

register

$24

(big-endian)

before

10234567

98101112131415

ABCDEFGH

address 0

address 8

0

981011121315

CDEFGHB

Loading...

Loading...