Appendix A

A-138 MIPS R4000 Microprocessor User's Manual

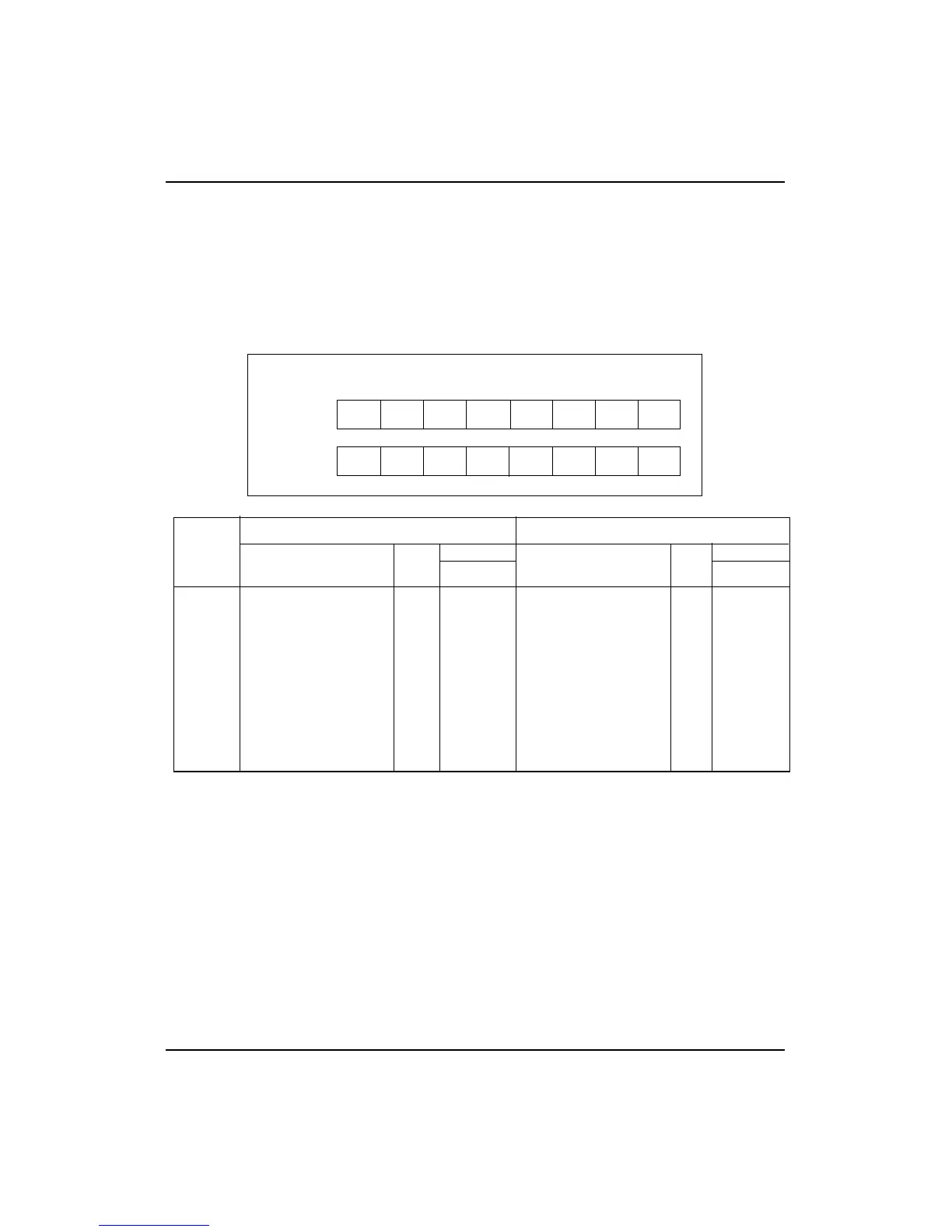

Given a doubleword in a register and a doubleword in memory, the

operation of SDR is as follows:

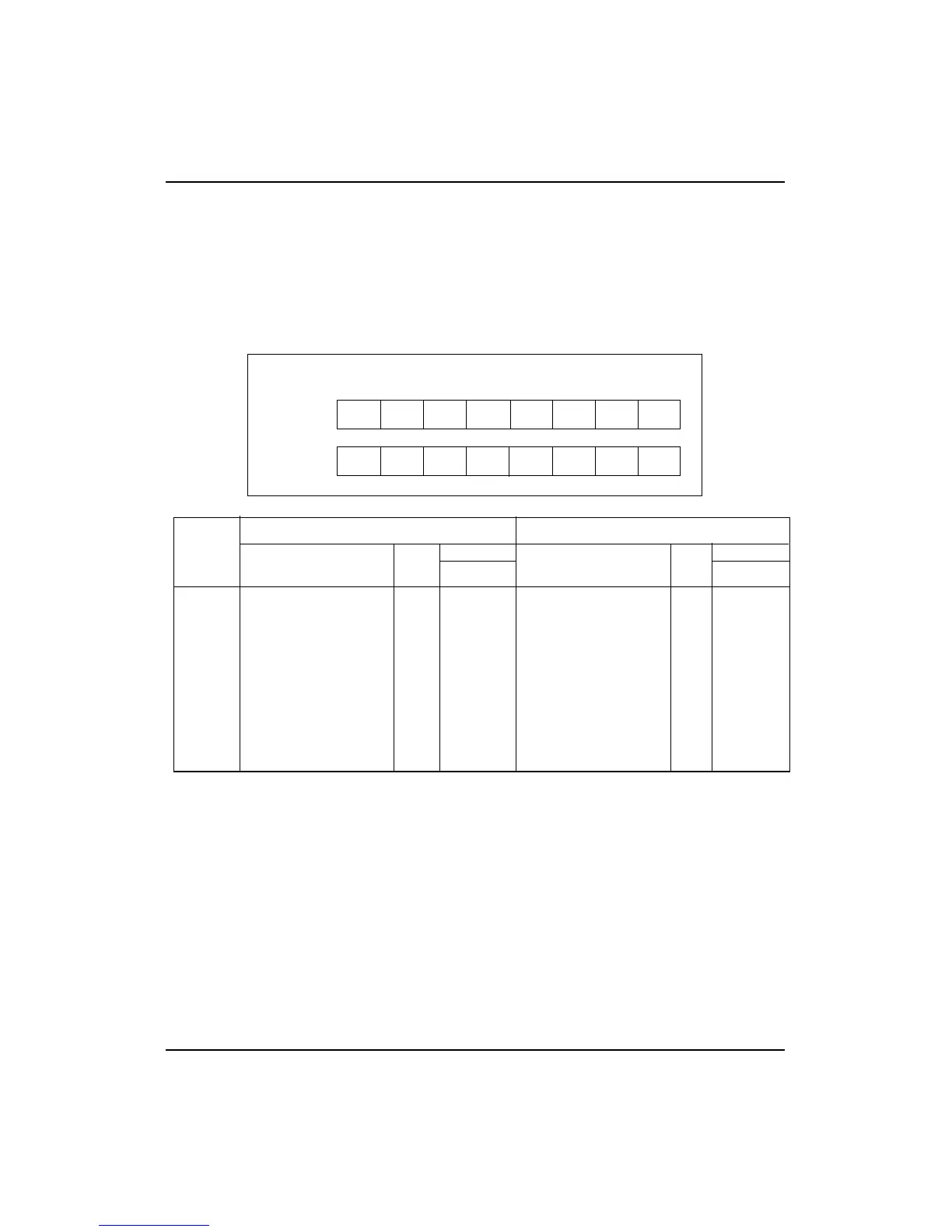

LEM Little-endian memory (BigEndianMem = 0)

BEM BigEndianMem = 1

Type AccessType (see Table 2-1) sent to memory

Offset pAddr

2...0

sent to memory

Exceptions:

TLB refill exception

TLB invalid exception

TLB modification exception

Bus error exception

Address error exception

Reserved instruction exception (R4000 in 32-bit mode)

SDR

Store Doubleword Right

SDR

(continued)

SDR

ACDB

Register

IKLJ

Memory

EGHF

MOPN

0ABCDEFGH700HJKLMNOP070

1BCDEFGHP610GHKLMNOP160

2CDEFGHOP520FGHLMNOP250

3DEFGHNOP430EFGHMNOP340

4EFGHMNOP340DEFGHNOP430

5FGHLMNOP250CDEFGHOP520

6GHKLMNOP160BCDEFGHP610

7HJKLMNOP070ABCDEFGH700

offset

BigEndianCPU = 1

BigEndianCPU = 0

offset

LEM BEM

LEM BEM

vAddr

2..0

type

destination

destination

type

Loading...

Loading...