MIPS R4000 Microprocessor User's Manual A-181

CPU Instruction Set Details

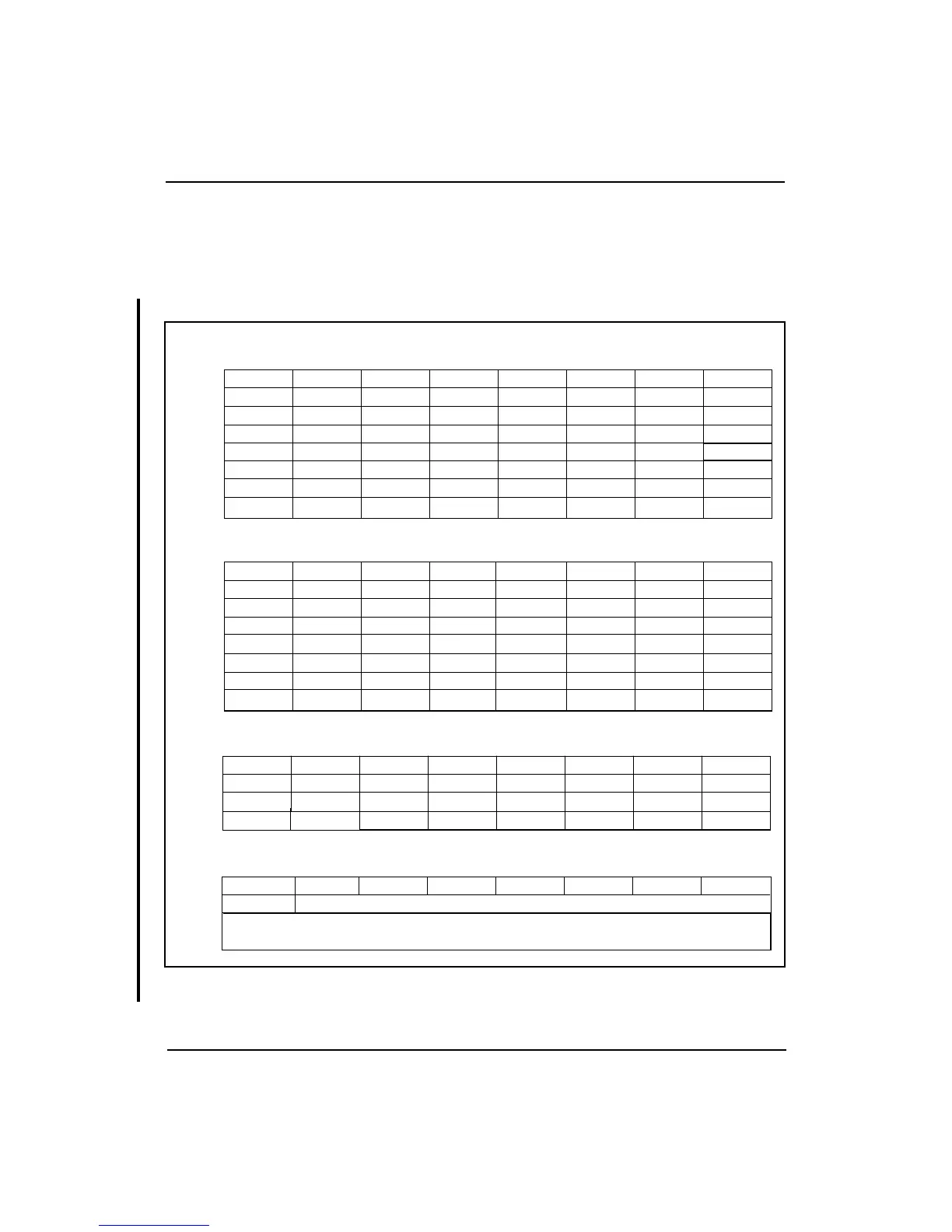

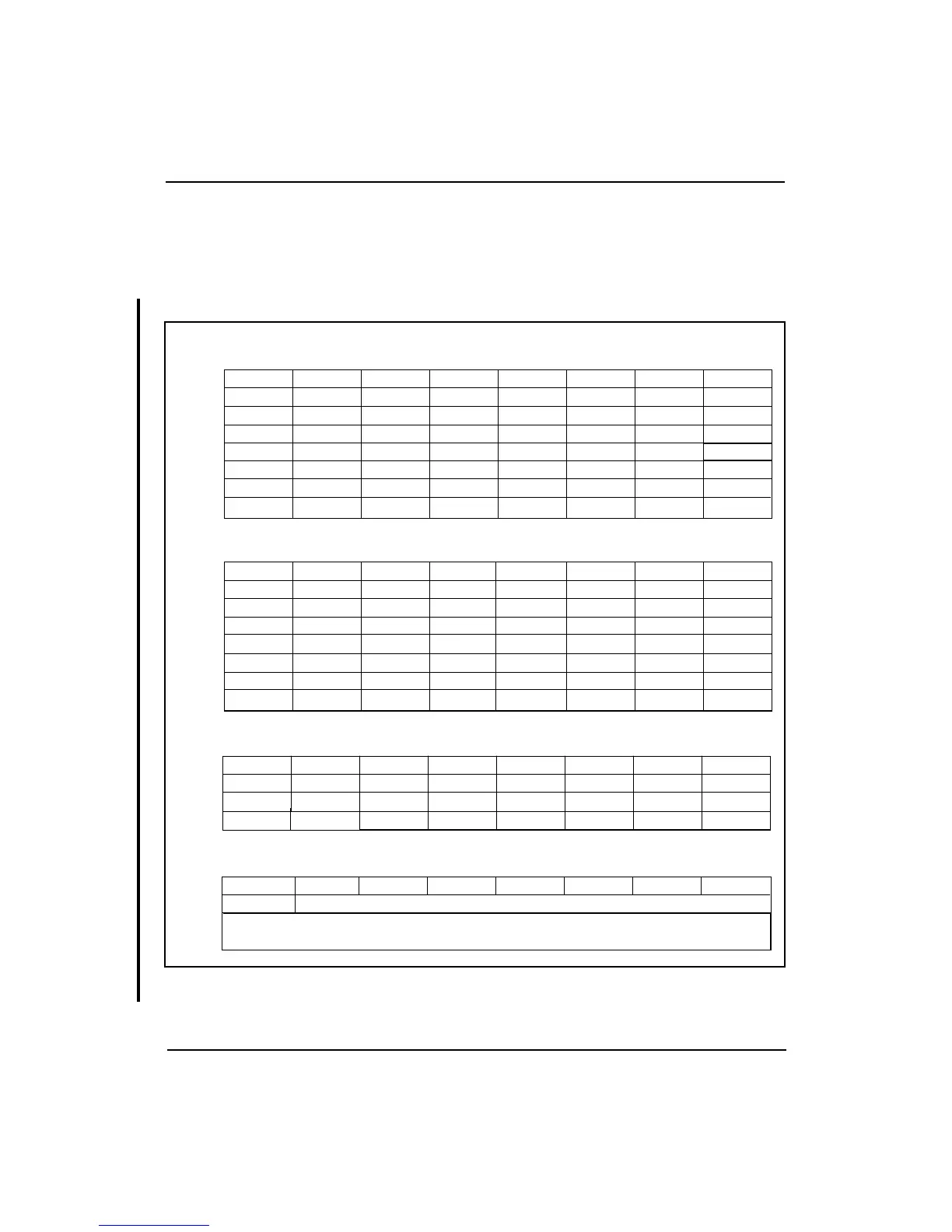

CPU Instruction Opcode Bit Encoding

The remainder of this Appendix presents the opcode bit encoding for the

CPU instruction set (ISA and extensions), as implemented by the R4000.

Figure A-2 lists the R4000 Opcode Bit Encoding.

Figure A-2 R4000 Opcode Bit Encoding

SPECIAL

ADDI

COP0

DADDIε DADDIUε LDLε LDRε

****

BEQL BNEL

BLEZL BGTZL

LB

SB

CACHE

LWUε

*

LL

LDC1 LDC2

LDε

SC

SDC1 SDC2 SDε

DSLLε * DSRLε DSRAε DSLL32ε * DSRL32ε DSRA32ε

TGE TGEU TLT TLTU TEQ TNE

2...0

REGIMM rt

18...16

SLL

JR

MFHI

MULT

ADD

SLT

*

DSLLVε * DSRLVε DSRAVε

DMULTε DMULTUε DDIVε DDIVUε

DADDε DADDUε DSUBε DSUBUε

**

*

COPz rs

SPECIAL function

01234567

0123 4 56 7

31...29

0

1

2

3

4

5

6

5...3

0

1

2

3

4

5

6

7

20...19

0

1

2

3

7

28...26

Opcode

01234 567

SYSCALL BREAK

SH SWL SW SWR

LWC1 LWC2 *

SWC1 SWC2

*

LH LWL LW LBU LHU LWR

SRL SRA SLLV SRLV SRAV

JALR

MTHI MFLO MTLO

MULTU DIV DIVU

ADDU SUB SUBU AND OR XOR NOR

SLTU

COP1 COP2

*

ADDIU SLTI SLTIU ANDI ORI XORI LUI

REGIMM J JAL BEQ BNE BLEZ BGTZ

*

*

BLTZL

TLTI

BLTZALL

BGEZL

TLTIU

BGEZALL

TNEI

TEQI

MF

23...21

01234567

25, 24

0

1

2

3

CF

BC

MT CT

CO

DMFεγ

DMTε

γ

SDLε

LLDε

SCDε

SDRε

**

SYNC

δ

γγ γ γ γγ γ

**** * ** *

****

****

**

BLTZ

BLTZAL

BGEZ

BGEZAL

TGEI TGEIU

Loading...

Loading...