MIPS R4000 Microprocessor User's Manual B-13

FPU Instruction Set Details

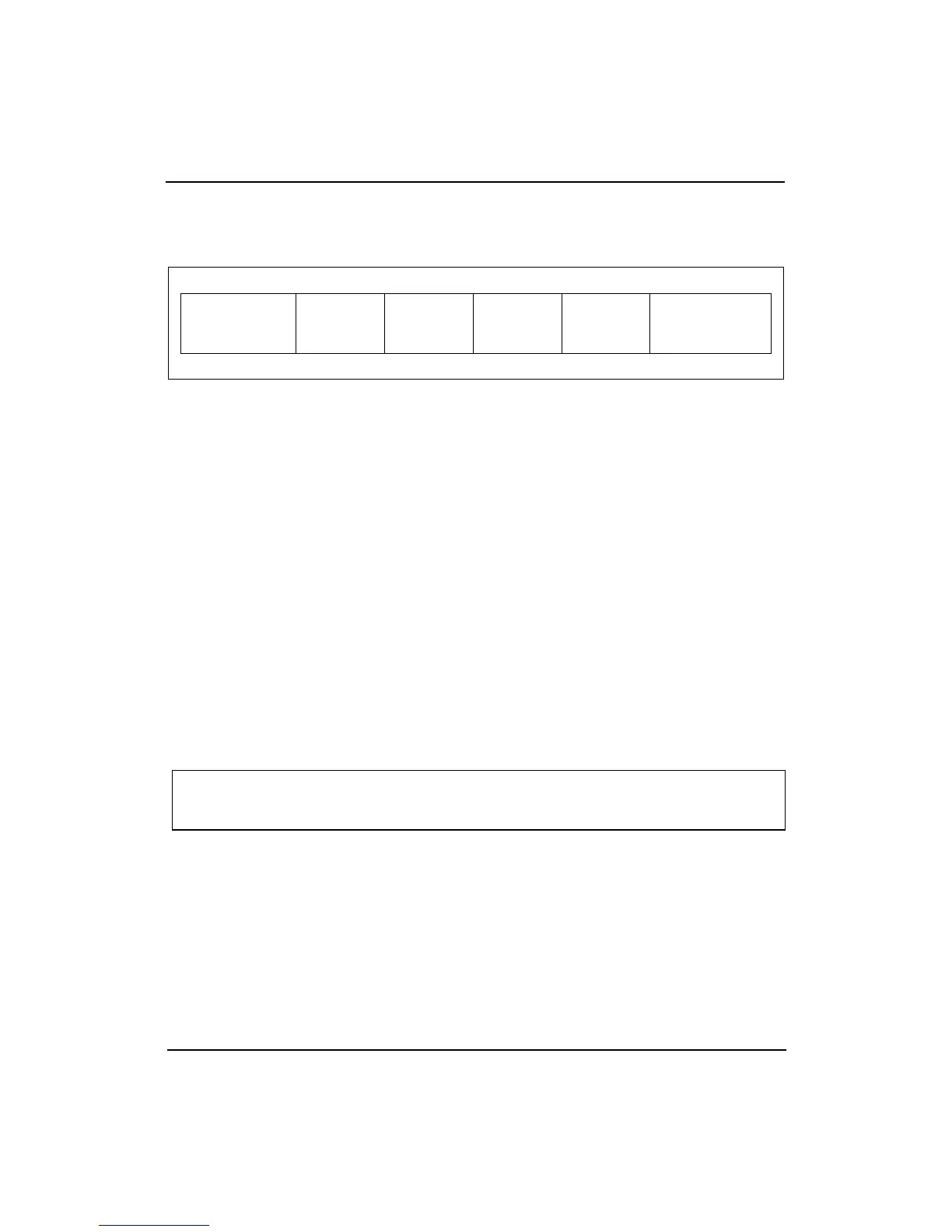

Format:

ABS.fmt fd, fs

Description:

The contents of the FPU register specified by fs are interpreted in the

specified format and the arithmetic absolute value is taken. The result is

placed in the floating-point register specified by fd.

The absolute value operation is arithmetic; a NaN operand signals invalid

operation.

This instruction is valid only for single- and double-precision floating-

point formats. The operation is not defined if bit 0 of any register

specification is set and the FR bit in the Status register equals zero, since

the register numbers specify an even-odd pair of adjacent coprocessor

general registers. When the FR bit in the Status register equals one, both

even and odd register numbers are valid.

Operation:

Exceptions:

Coprocessor unusable exception

Coprocessor exception trap

Coprocessor Exceptions:

Unimplemented operation exception

Invalid operation exception

ABS.fmt

Floating-Point

31 0

655556

COP1 fmt 0 fs fd ABS

11 1021 20 16 1526 25 6 5

0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 1

ABS.fmt

Absolute Value

T: StoreFPR(fd, fmt, AbsoluteValue(ValueFPR(fs, fmt)))

Loading...

Loading...