CMS32L051 User Manual |Chapter 12 Universal Serial Communication Unit

www.mcu.com.cn 315 / 703

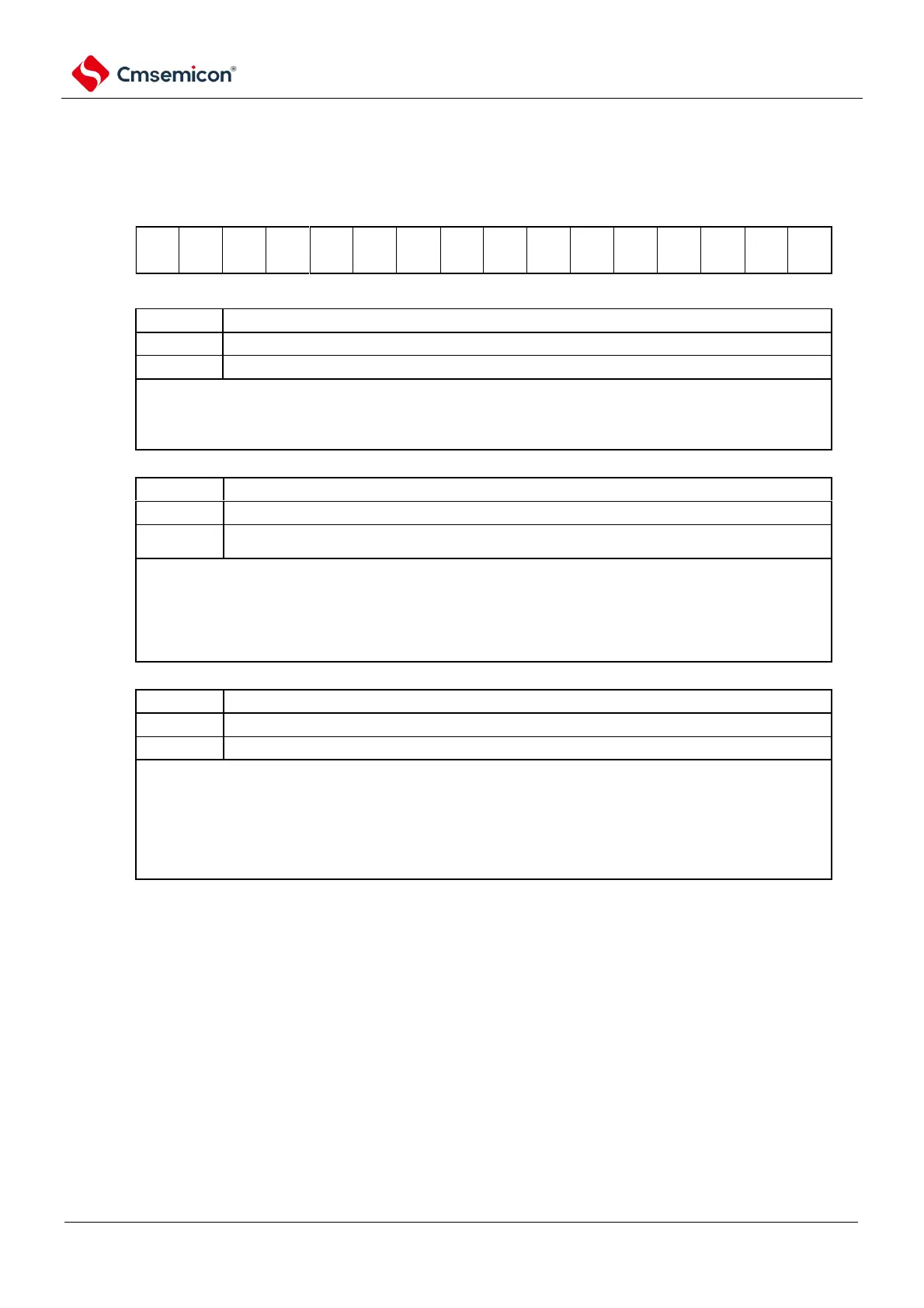

Figure 12-11 Format of serial status register mn (SSRmn) (2/2)

Address: 40041100H (SSR00) ~ 40041106H (SSR03) After reset: 0000HR

40041540H(SSR10)~40041542H(SSR11)

Symbol

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SSRmn

Detection flag for channel n frame errors

An error occurred (when the UART was received).

[Clear condition].

writing 1 to the FECTmn bit of the SIRmn register

[Accent condition].

stop bit is detected at the end of UART reception

Detection flag for channel n parity errors

An error occurred (when the UART was received) or the ACK was not detected (when the I2C

was sent).

[Clear condition].

writing 1 to the PECTmn bit of the SIRmn register

[Set condition].

the parity and parity bits of the data sent at the end of the UART reception are different (parity errors).

When it is sent by I2C and when the ACK receiving timing slave does not return an ACK signal (no ACK

detected).

Detection flag for channel n overflow error

[Clear condition].

writing 1 to the OVCTmn bit of the SIRmn register

[Set condition].

the state where the RXEmn bit of the SCRmn register is 1 (receive mode, transmit and receive modes in

each communication mode), although the received data is saved in the SDRmn register, but when there is no

read receive data and write send data or write down a received data

When data is not ready to be sent during slave send or slave send and receive in SSPI mode.

Note 1 For SSR01, SSR03, SSR11 registers only.

Notice 1 If you write the SDRmn register when the BFFmn bit is 1, the saved transmit or receive data is corrupted and

an overflow error is detected (OVEmn=1).

Remark m: unit number (m=0, 1) n: channel number (n=0~3).

Loading...

Loading...