CMS32L051 User Manual |Chapter 12 Universal Serial Communication Unit

www.mcu.com.cn 382 / 703

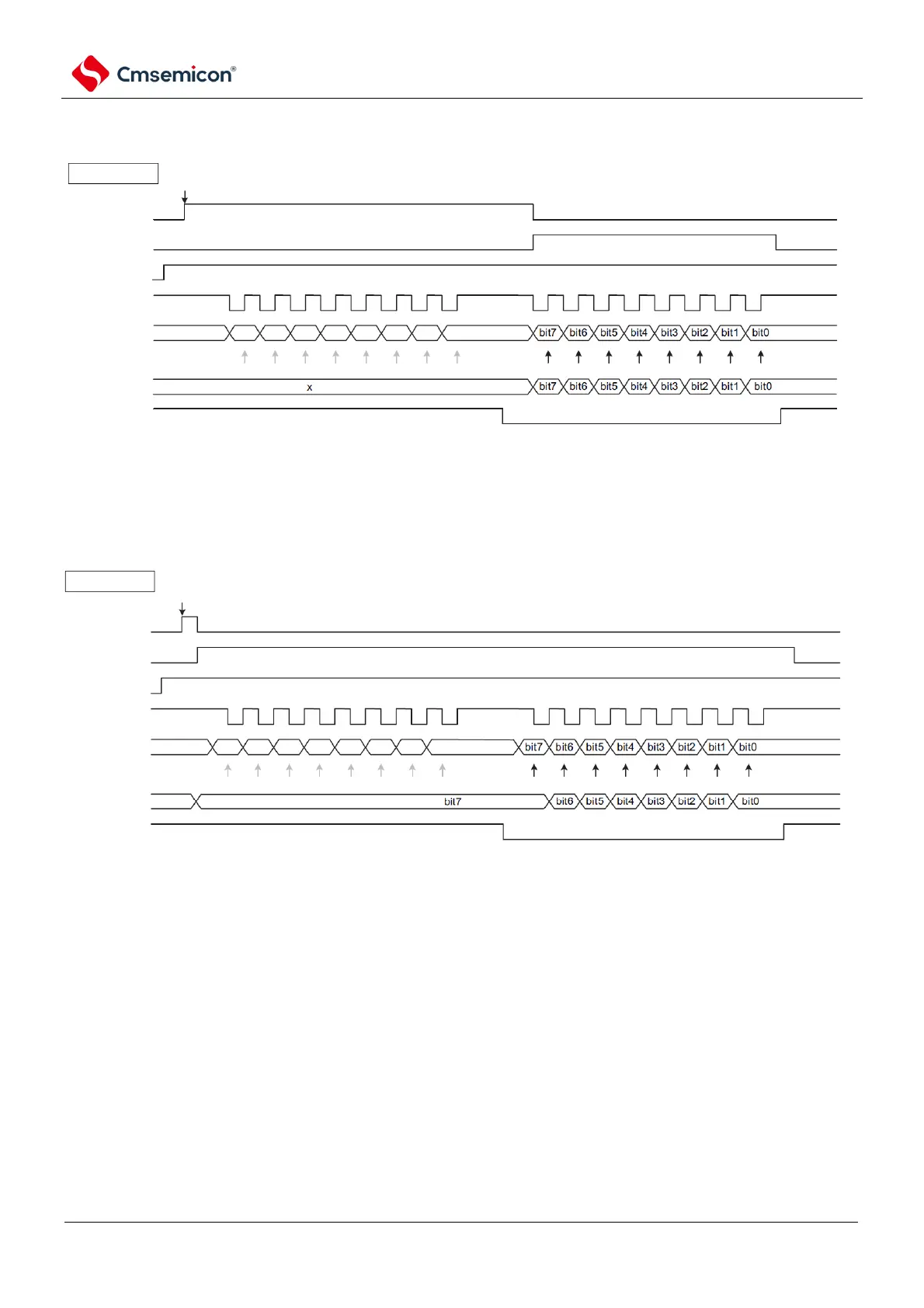

Figure 12-71 Slave timing diagram of the select input function

SSmn

SDOmn

sample timing sequence

SDImn

SCLKmn

(CKPmn=0)

SSEmn

TSFmn

BFFmn

configure transmit data

DAPmn=0

During SSmn is high, even on the falling edge of the SCKmn (serial clock), no transmission occurs, and

no sampling of received data synchronized with the rising edge is taken.

During SSmn low, the output data is synchronized (shifted) with the falling edge of the serial clock and

received synchronously with the rising edge.

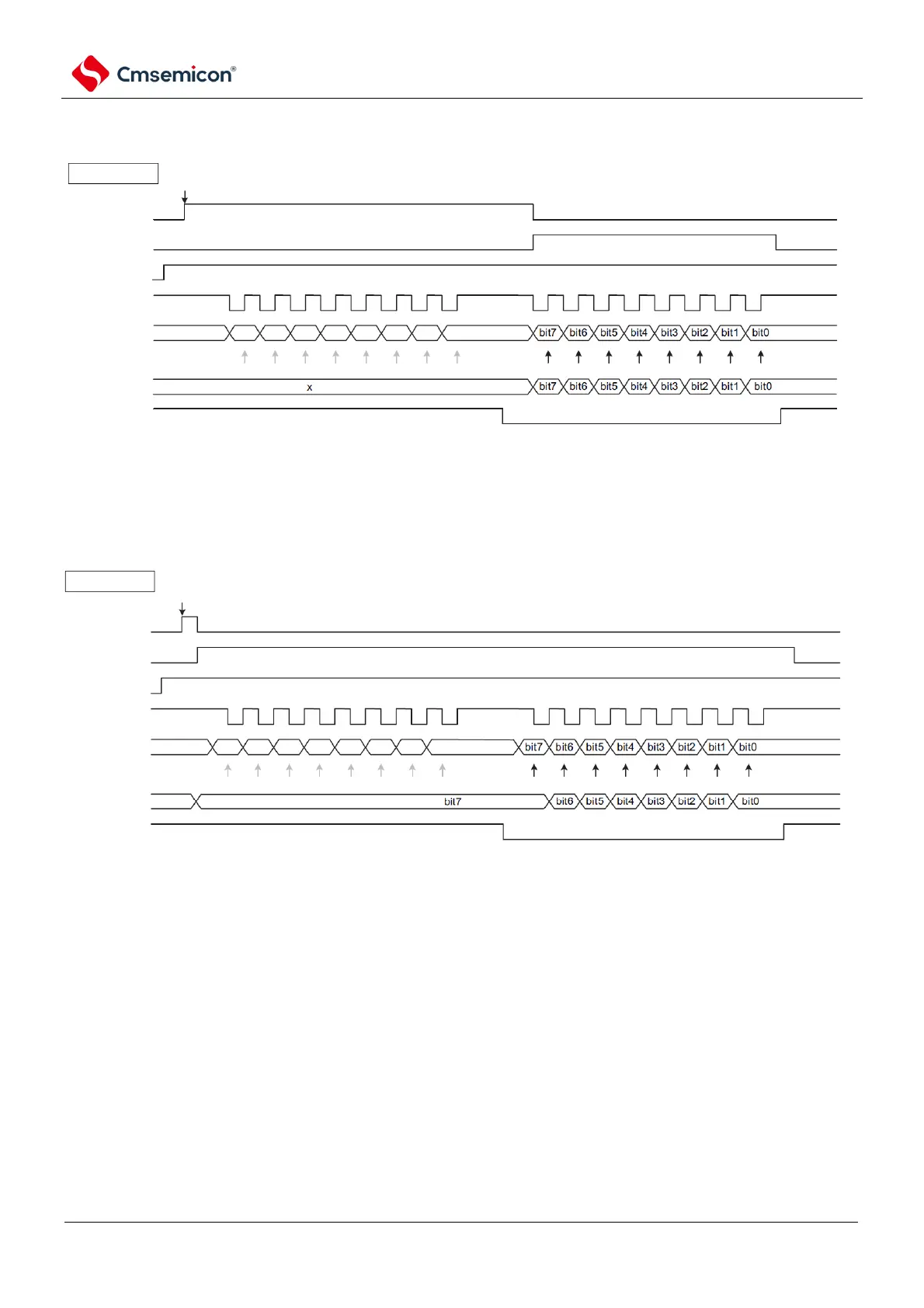

SSmn

SDOmn

sample timing sequence

SDImn

SCLKmn

(CKPmn=0)

SSEmn

TSFmn

BFFmn

configure transmit data

DAPmn=1

When the DAPmn bit is 1, the initial data (bit7) is supplied to the data output if the transmit data is set

during when SSmn is high. However, even the rising edge of the SCLK mn (serial clock) is not shifted, and the

accepted data synchronized with the falling edge is not sampled. If SSmn goes low, the output data is

synchronized (shifted) with the next rising edge and received synchronously with the falling edge.

Remark m: Unit number (m=0) n: Channel number (n=0).

Loading...

Loading...