Real-time clock (RTC) RM0453

1028/1461 RM0453 Rev 1

32.6.10 RTC shift control register (RTC_SHIFTR)

This register is write protected. The write access procedure is described in RTC register

write protection on page 1007.

Address offset: 0x2C

Backup domain reset value: 0x0000 0000

System reset: not affected

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 CALP: Increase frequency of RTC by 488.5 ppm

0: No RTCCLK pulses are added.

1: One RTCCLK pulse is effectively inserted every 2

11

pulses (frequency increased by

488.5 ppm).

This feature is intended to be used in conjunction with CALM, which lowers the frequency of

the calendar with a fine resolution. if the input frequency is 32768 Hz, the number of

RTCCLK pulses added during a 32-second window is calculated as follows: (512 × CALP) -

CALM.

Refer to Section 32.3.14: RTC smooth digital calibration.

Bit 14 CALW8: Use an 8-second calibration cycle period

When CALW8 is set to 1, the 8-second calibration cycle period is selected.

Note: CALM[1:0] are stuck at 00 when CALW8 = 1. Refer to Section 32.3.14: RTC smooth

digital calibration.

Bit 13 CALW16: Use a 16-second calibration cycle period

When CALW16 is set to 1, the 16-second calibration cycle period is selected. This bit must

not be set to 1 if CALW8 = 1.

Note: CALM[0] is stuck at 0 when CALW16 = 1. Refer to Section 32.3.14: RTC smooth digital

calibration.

Bit 12 LPCAL: Calibration low-power mode

0:Calibration window is 2

20

RTCCLK, which is a high-consumption mode. This mode should

be set only when less than 32s calibration window is required.

1:Calibration window is 2

20

ck_apre, which is the required configuration for ultra-low

consumption mode.

Bits 11:9 Reserved, must be kept at reset value.

Bits 8:0 CALM[8:0]: Calibration minus

The frequency of the calendar is reduced by masking CALM out of 2

20

RTCCLK pulses (32

seconds if the input frequency is 32768 Hz). This decreases the frequency of the calendar

with a resolution of 0.9537 ppm.

To increase the frequency of the calendar, this feature should be used in conjunction with

CALP. See Section 32.3.14: RTC smooth digital calibration on page 1012.

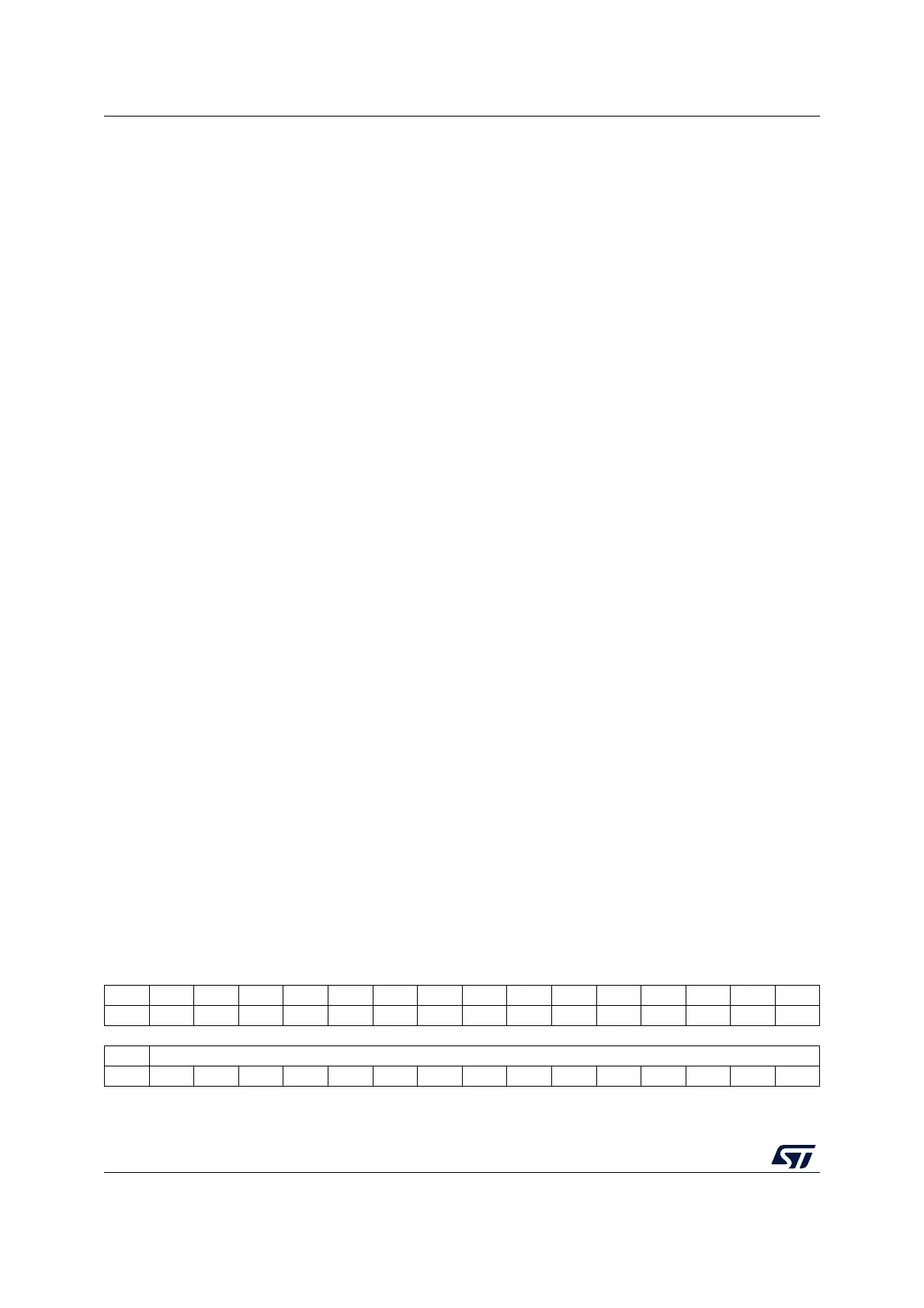

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ADD1S Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

w

1514131211109876543210

Res. SUBFS[14:0]

wwwwwwwwwwwwwww

Loading...

Loading...