Voltage reference buffer (VREFBUF) RM0453

620/1461 RM0453 Rev 1

20.3 VREFBUF registers

20.3.1 VREFBUF control and status register (VREFBUF_CSR)

Address offset: 0x00

Reset value: 0x0000 0002

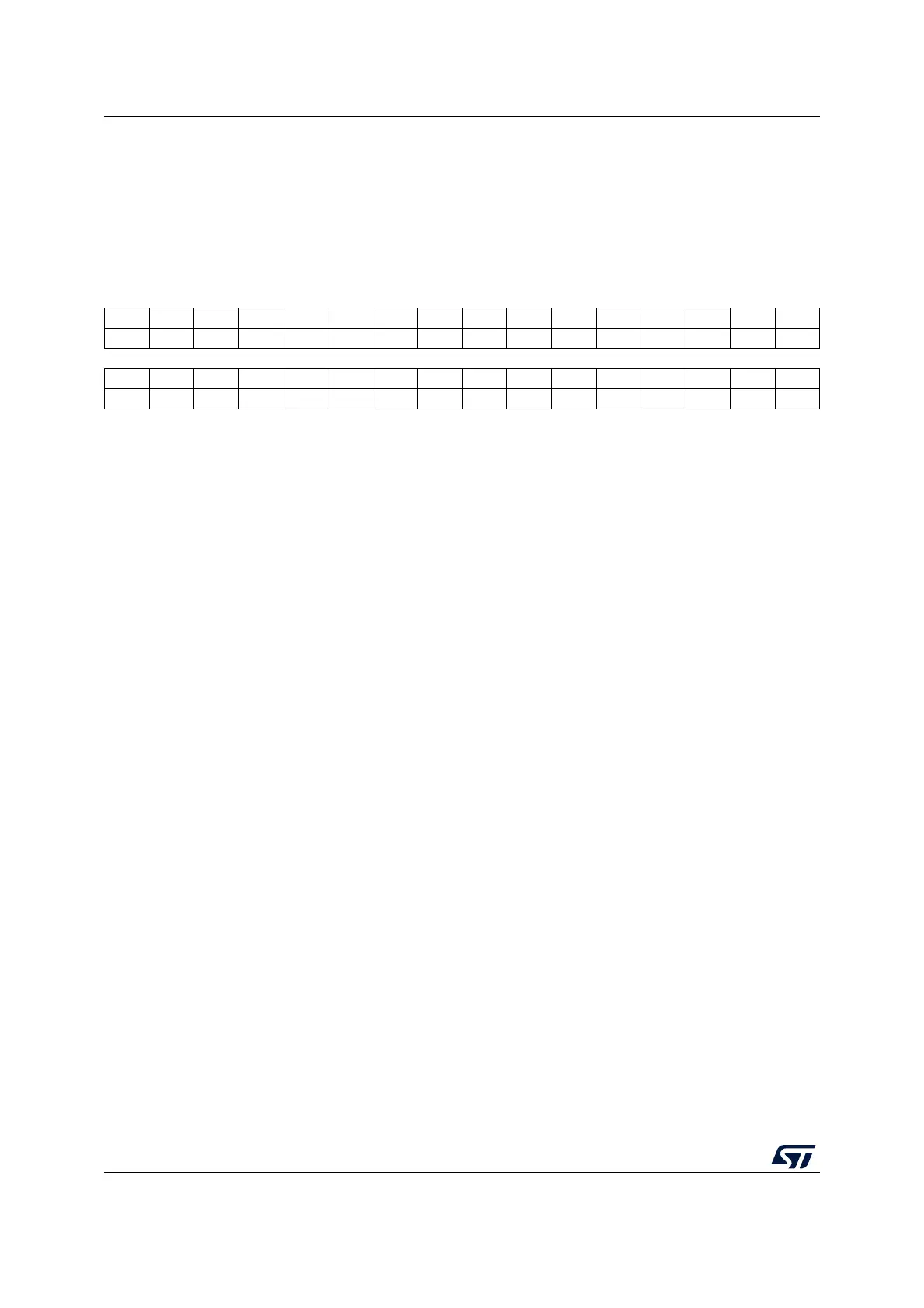

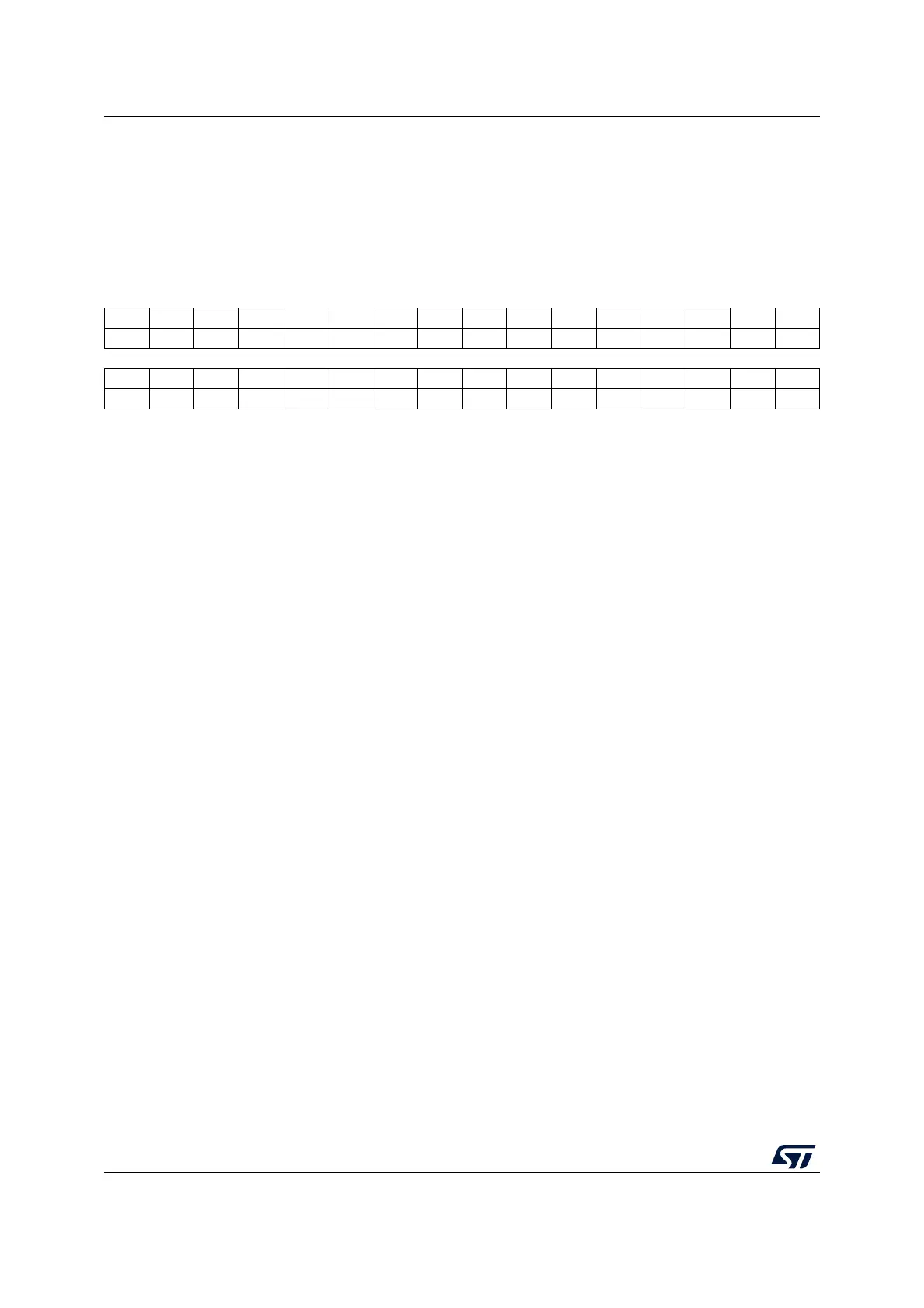

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. VRR VRS HIZ ENVR

rrwrwrw

Bits 31:4 Reserved, must be kept at reset value.

Bit 3 VRR: Voltage reference buffer ready

0: the voltage reference buffer output is not ready.

1: the voltage reference buffer output reached the requested level.

Bit 2 VRS: Voltage reference scale

This bit selects the value generated by the voltage reference buffer.

0: Voltage reference set to V

REF_OUT1

(around 2.048 V).

1: Voltage reference set to V

REF_OUT2

(around 2.5 V).

Bit 1 HIZ: High impedance mode

This bit controls the analog switch to connect or not the V

REF+

pin.

0: V

REF+

pin is internally connected to the voltage reference buffer output.

1: V

REF+

pin is high impedance.

Refer to Table 120: VREF buffer modes for the mode descriptions depending on ENVR bit

configuration.

Bit 0 ENVR: Voltage reference buffer mode enable

This bit is used to enable the voltage reference buffer mode.

0: Internal voltage reference mode disable (external voltage reference mode).

1: Internal voltage reference mode (reference buffer enable or hold mode) enable.

Loading...

Loading...