RM0453 Rev 1 257/1461

RM0453 Power control (PWR)

276

6.6.3 PWR control register 3 (PWR_CR3)

This register is not reset when exiting Standby modes.

Access: additional APB cycles are needed to access this register versus those needed for a

standard APB access (three for a write and two for a read).

Address offset: 0x008

Reset value: 0x0000 8000

Bits 3:1 PLS[2:0]: Power voltage detector level selection.

These bits select the voltage threshold detected by the power voltage detector:

000: V

PVD0

around 2.0 V

001: V

PVD1

around 2.2 V

010: V

PVD2

around 2.4 V

011: V

PVD3

around 2.5 V

100: V

PVD4

around 2.6 V

101: V

PVD5

around 2.8 V

110: V

PVD6

around 2.9 V

111: External input analog voltage PVD_IN (compared internally to VREFINT)

Note: These bits are write-protected when the bit PVDL (PVD Lock) is set in the

SYSCFG_CBR register.

These bits are reset only by a system reset.

Bit 0 PVDE: Power voltage detector enable

0: Power voltage detector disabled

1: Power voltage detector enabled

Note: This bit is write-protected when the bit PVDL (PVD Lock) is set in the SYSCFG_CBR

register.

This bit is reset only by a system reset.

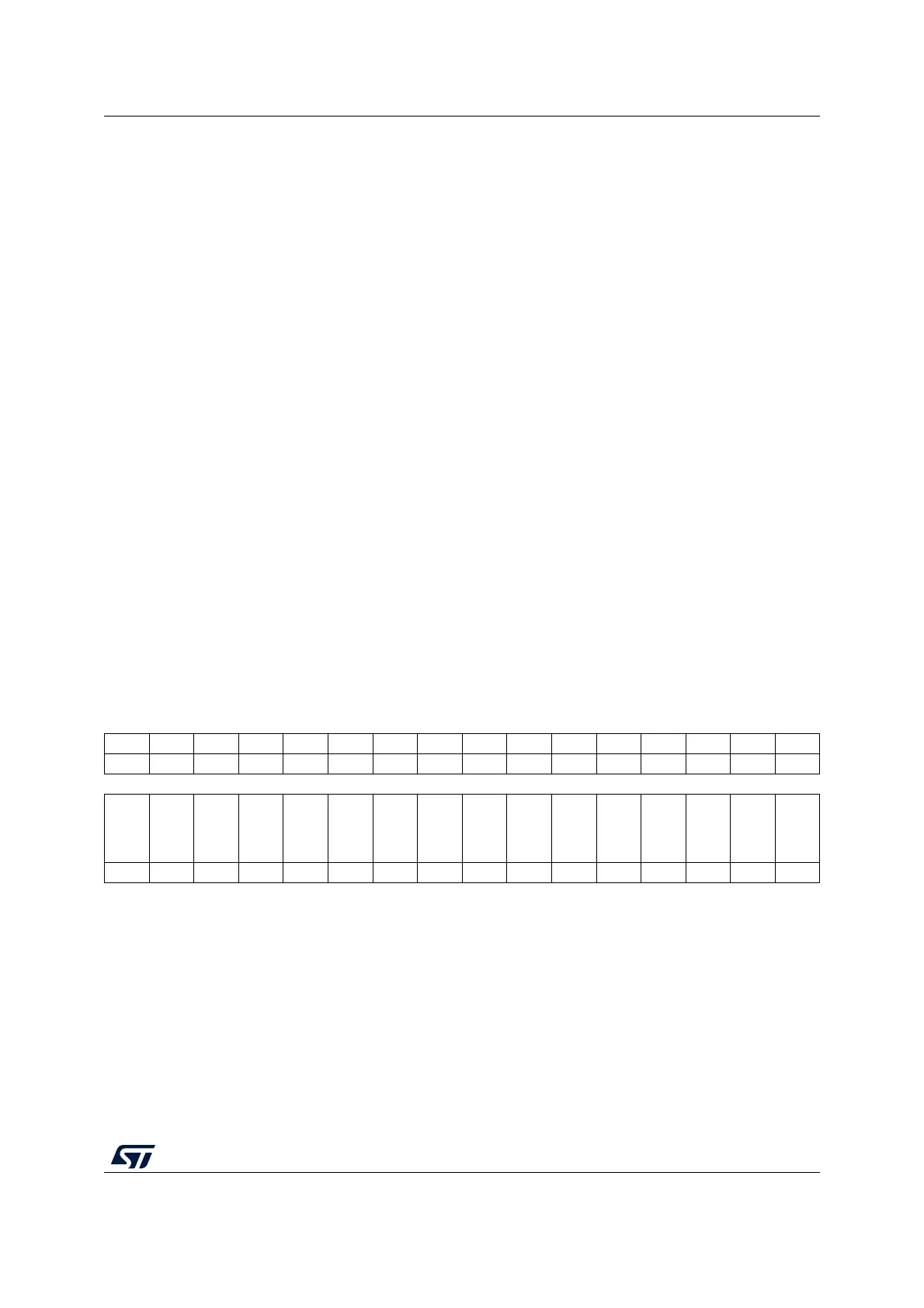

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

EIWUL EC2H

EWRFIRQ

Res.

EWRFBUSY

APC RRS

EWPVD

ULPEN Res. Res. Res. Res.

EWUP3

EWUP2

EWUP1

rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 EIWUL: internal wakeup line for CPU1 enable

0: Internal wakeup line interrupt to CPU1 disabled

1: Internal wakeup line interrupt to CPU1 enabled

Bit 14 EC2H: CPU2 hold interrupt for CPU1 enable

Enable CPU2 kept in hold, due to C2BOOT, interrupt to CPU1.

0: Interrupt to CPU1 disabled

1: interrupt to CPU1 enabled

Loading...

Loading...