RM0453 Rev 1 969/1461

RM0453 Low-power timer (LPTIM)

981

28.7 LPTIM registers

28.7.1 LPTIM interrupt and status register (LPTIM_ISR)

Address offset: 0x000

Reset value: 0x0000 0000

Update Event

Interrupt flag is raised when the repetition counter underflows (or contains

zero) and the LPTIM counter overflows.

Repetition register

update Ok

REPOK is set by hardware to inform application that the APB bus write

operation to the LPTIM_RCR register has been successfully completed.

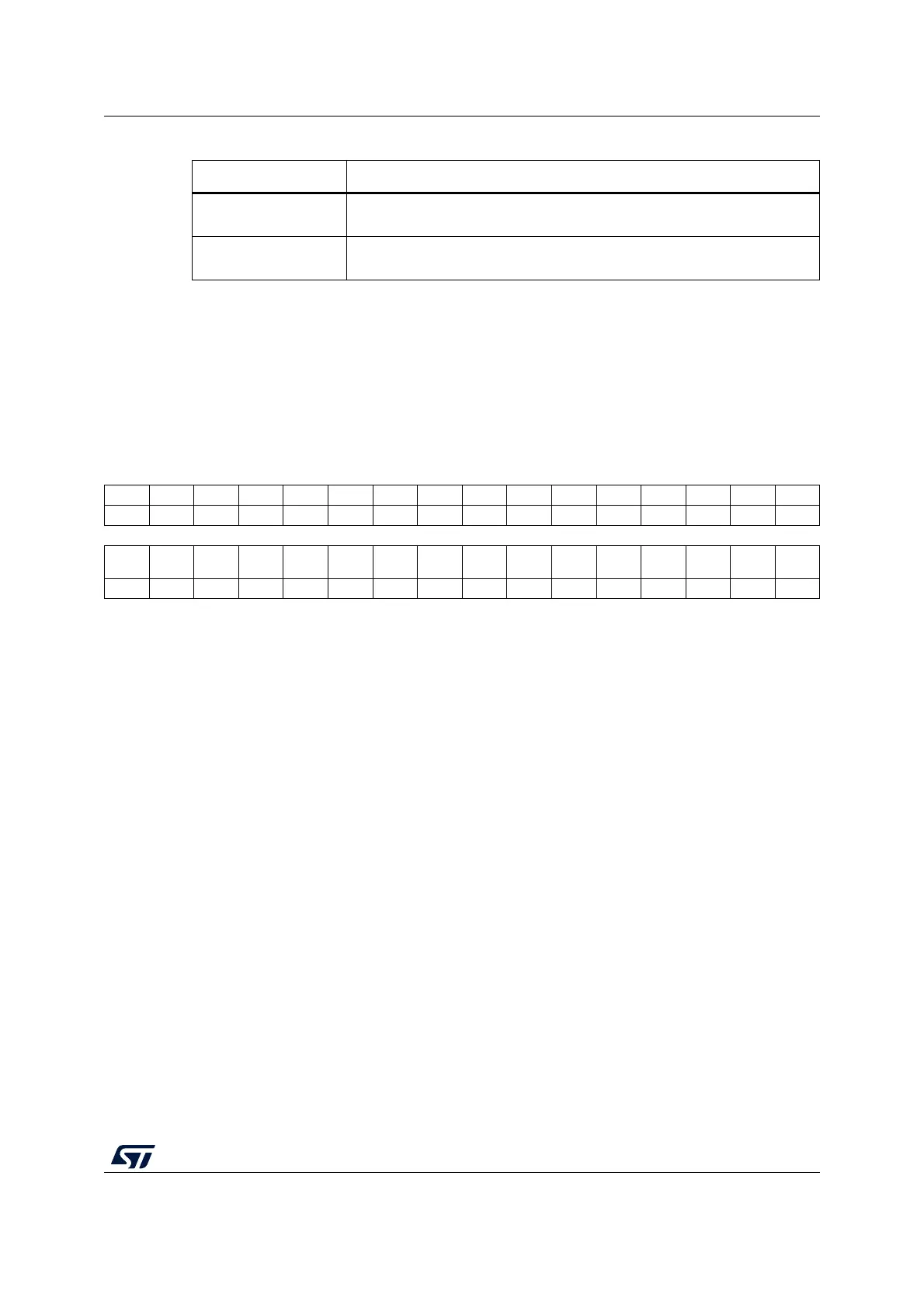

Table 202. Interrupt events (continued)

Interrupt event Description

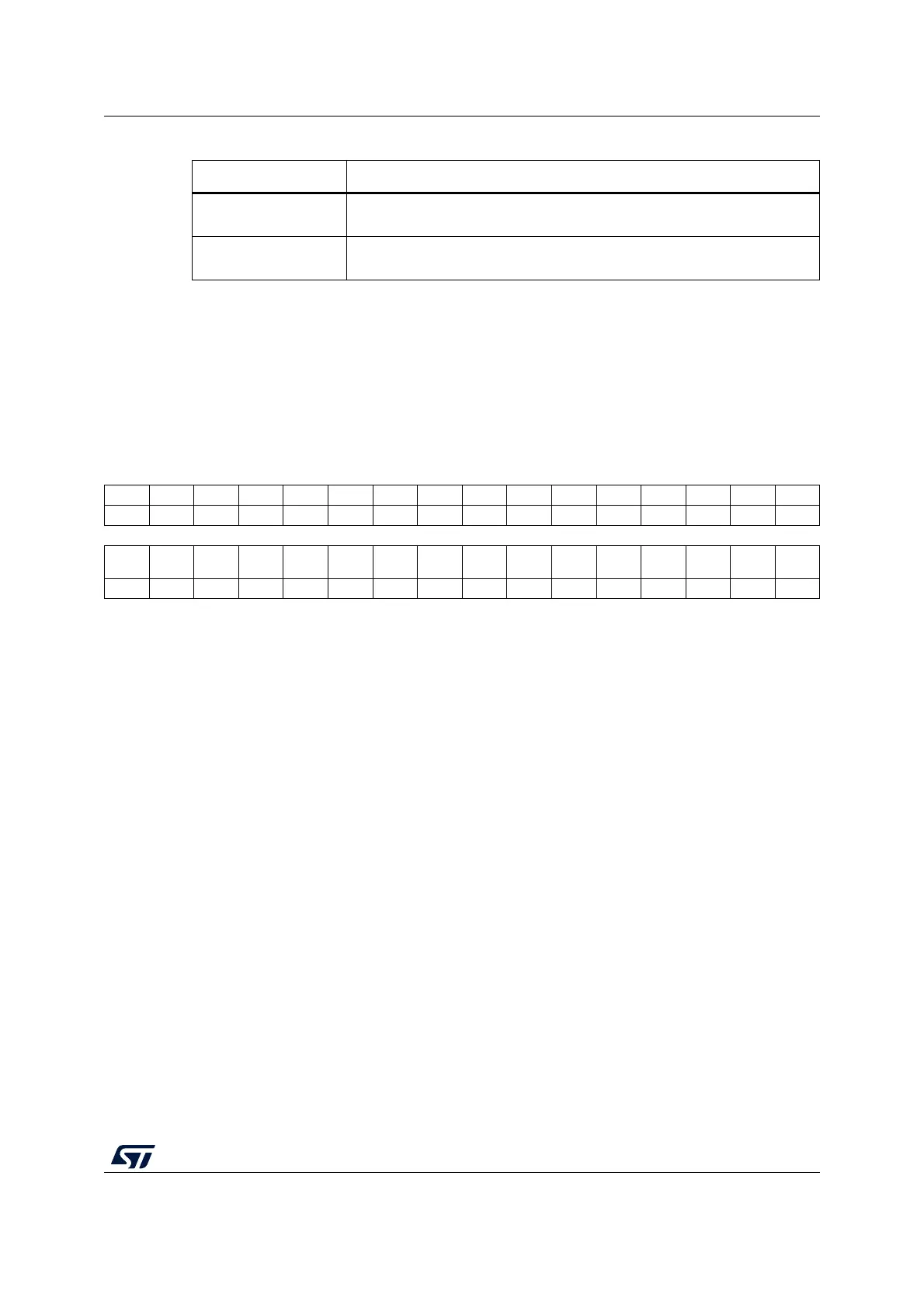

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res.

REP

OK

UE DOWN UP

ARR

OK

CMP

OK

EXT

TRIG

ARRM CMPM

rrrrrrrrr

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 REPOK: Repetition register update Ok

REPOK is set by hardware to inform application that the APB bus write operation to the LPTIM_RCR

register has been successfully completed. REPOK flag can be cleared by writing 1 to the REPOKCF

bit in the LPTIM_ICR register.

Bit 7 UE: LPTIM update event occurred

UE is set by hardware to inform application that an update event was generated. UE flag can be

cleared by writing 1 to the UECF bit in the LPTIM_ICR register.

Bit 6 DOWN: Counter direction change up to down

In Encoder mode, DOWN bit is set by hardware to inform application that the counter direction has

changed from up to down. DOWN flag can be cleared by writing 1 to the DOWNCF bit in the

LPTIM_ICR register.

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 28.3: LPTIM implementation.

Bit 5 UP: Counter direction change down to up

In Encoder mode, UP bit is set by hardware to inform application that the counter direction has

changed from down to up. UP flag can be cleared by writing 1 to the UPCF bit in the LPTIM_ICR

register.

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 28.3: LPTIM implementation.

Bit 4 ARROK: Autoreload register update OK

ARROK is set by hardware to inform application that the APB bus write operation to the LPTIM_ARR

register has been successfully completed. ARROK flag can be cleared by writing 1 to the ARROKCF

bit in the LPTIM_ICR register.

Loading...

Loading...