RM0453 Rev 1 355/1461

RM0453 Reset and clock control (RCC)

364

7.4.45 RCC CPU2 APB2 peripheral clock enable in Sleep mode register

(RCC_C2APB2SMENR)

Address offset: 0x180

Reset value: 0x0006 5A00

Access: word, half-word and byte access

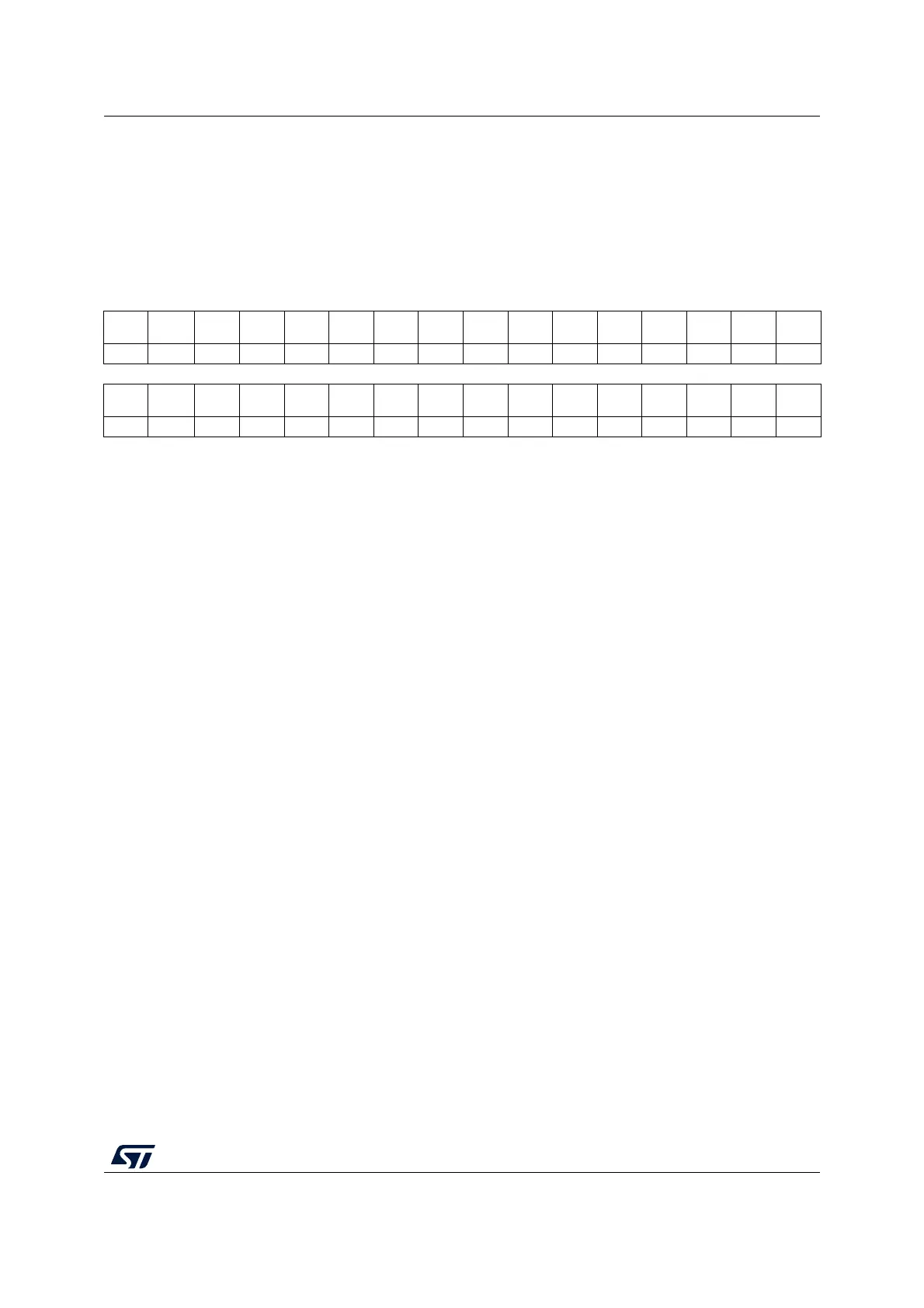

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

TIM17

SMEN

TIM16

SMEN

Res.

rw rw

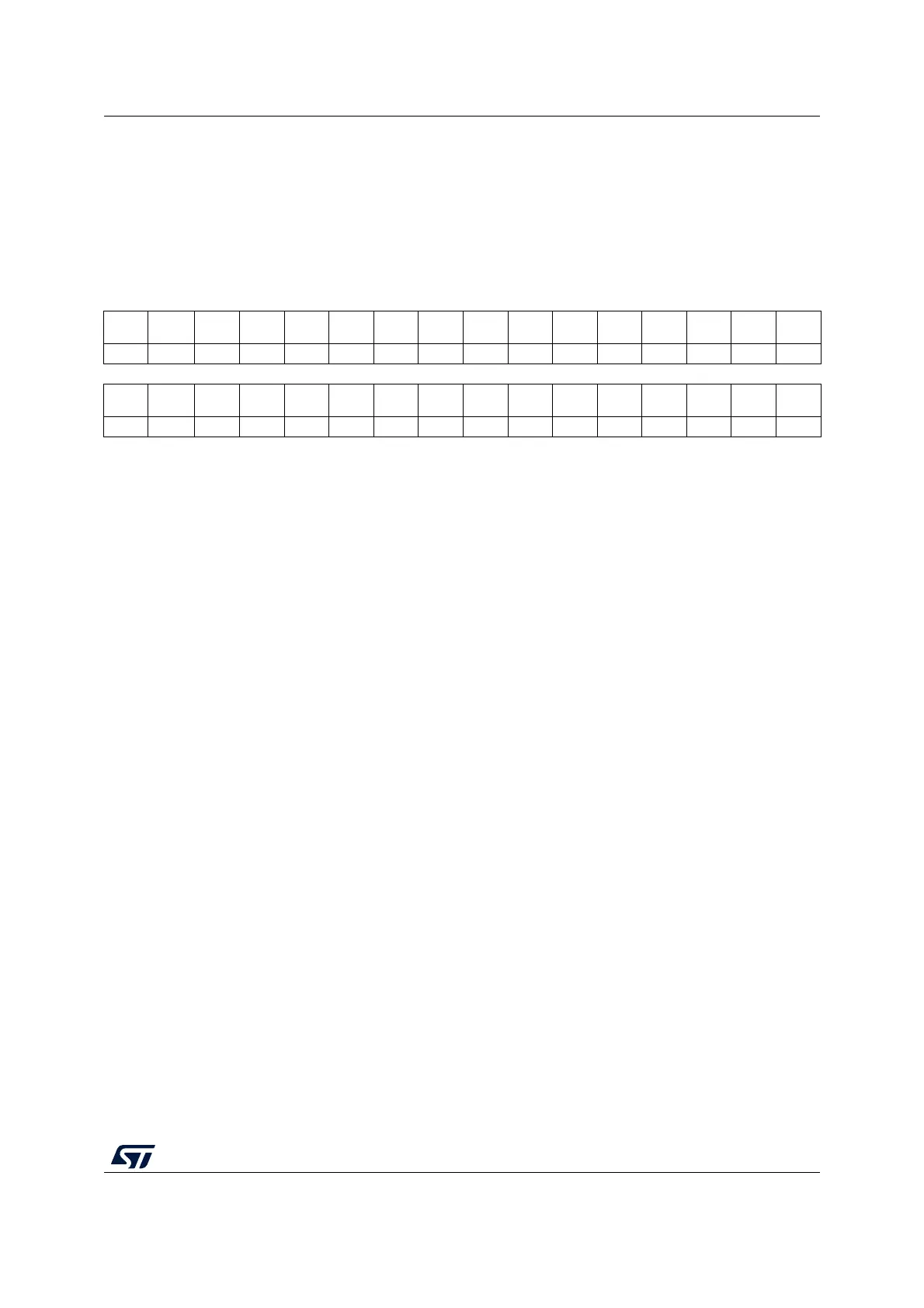

1514131211109876543210

Res.

USART1

SMEN

Res.

SPI1

SMEN

TIM1

SMEN

Res.

ADC

SMEN

Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw rw rw

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 TIM17SMEN: TIM17 timer clock enable during CPU2 CSleep and CStop modes

This bit is set and cleared by software.

0: TIM17 timer clock disabled by the clock gating during CPU2 CSleep and CStop modes

1: TIM17 timer clock enabled by the clock gating during CPU2 CSleep mode, disabled during

CPU2 CStop mode

Bit 17 TIM16SMEN: TIM16 timer clock enable during CPU2 CSleep and CStop modes

This bit is set and cleared by software.

0: TIM16 timer clock disabled by the clock gating during CPU2 CSleep and CStop modes

1: TIM16 timer clock enabled by the clock gating during CPU2 CSleep mode, disabled during

CPU2 CStop mode

Bits 16:15 Reserved, must be kept at reset value.

Bit 14 USART1SMEN: USART1clock enable during CPU2 CSleep and CStop modes

This bit is set and cleared by software.

0: USART1 bus clock disabled by the clock gating during CPU2 CSleep and CStop modes

1: USART1 bus clock enabled by the clock gating during CPU2 CSleep mode, disabled

during CPU2 CStop mode

Bit 13 Reserved, must be kept at reset value.

Bit 12 SPI1SMEN: SPI1 clock enable during CPU2 CSleep and CStop modes

This bit is set and cleared by software.

0: SPI1 clock disabled by the clock gating during CPU2 CSleep and CStop modes

1: SPI1 clock enabled by the clock gating during CPU2 CSleep mode, disabled during CPU2

CStop mode

Bit 11 TIM1SMEN: TIM1 timer clock enable during CPU2 CSleep and CStop modes

This bit is set and cleared by software.

0: TIM1 timer clock disabled by the clock gating during CPU2 CSleep and CStop modes

1: TIM1 timer clock enabled by the clock gating during CPU2 CSleep mode, disabled during

CPU2 CStop mode

Loading...

Loading...