RM0453 Rev 1 215/1461

RM0453 Sub-GHz radio (SUBGHZ)

218

5.10.25 Sub-GHz radio HSE32 OSC_OUT capacitor trim register

(SUBGHZ_HSEOUTTRIMR)

Address offset: 0x0912

Reset value: 0x12

This register is retained in Sleep mode, but lost in Deep-Sleep mode.

5.10.26 Sub-GHz radio SMPS control 0 register (SUBGHZ_SMPSC0R)

Address offset: 0x0916

Reset value: 0x00

Bits 7:6 Reserved, must be kept at reset value.

Bits 5:0 TRIM[5:0]: HSE32 XTAL mode OSC_IN load capacitor trimming

Load capacitor trimming step size ~0.47 pf.

0x00: minimum value ~11.3 pF

...

0x12 value ~20.3 pF (default)

...

0x2F: maximum capacitor value ~33.4 pF

Others: reserved

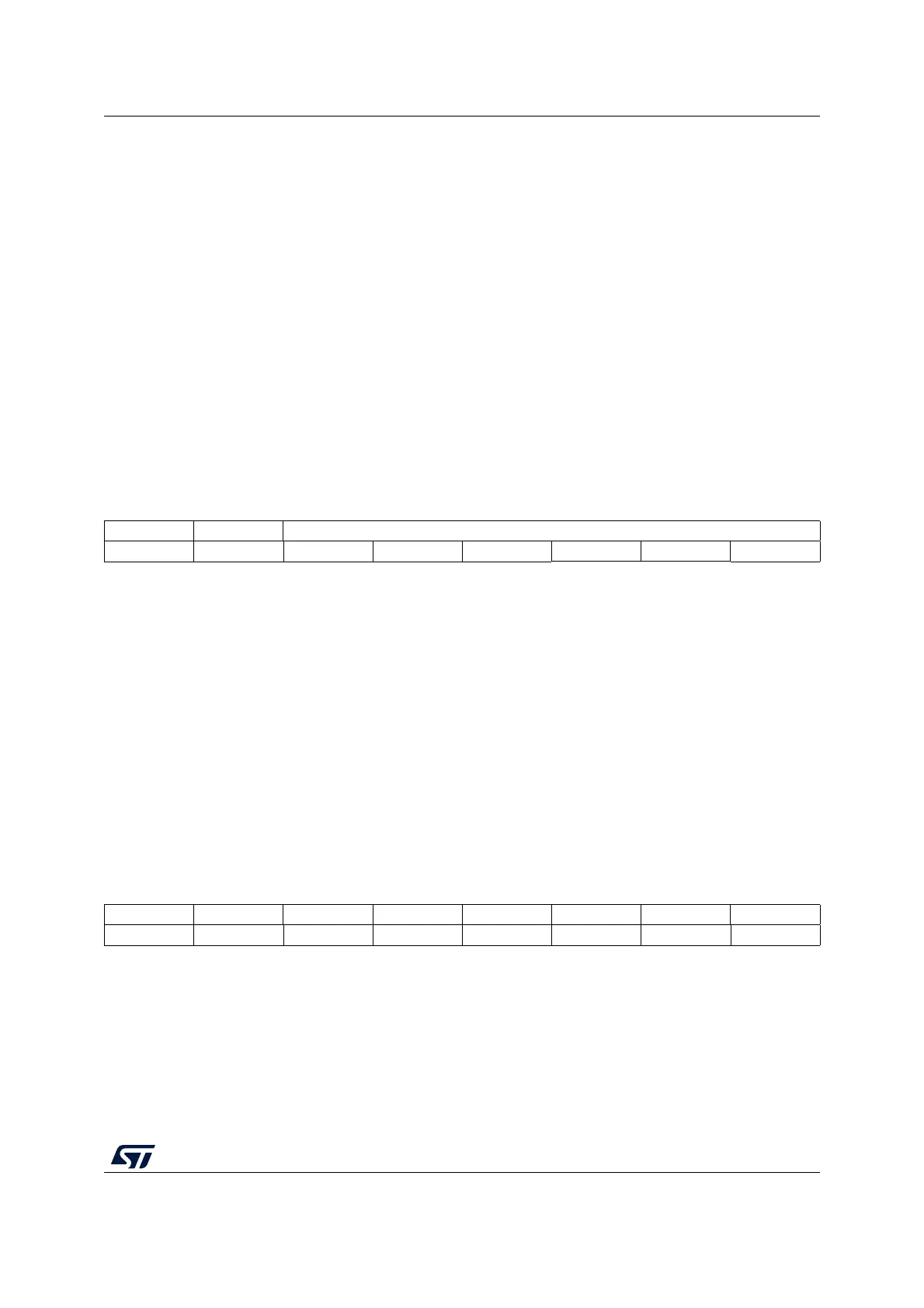

76543210

Res. Res. TRIM[5:0]

rw rw rw rw rw rw

Bits 7:6 Reserved, must be kept at reset value.

Bits 5:0 TRIM[5:0]: HSE32 XTAL mode OSC_OUT load capacitor trimming

Load capacitor trimming step size ~0.47 pf.

0x00: minimum value ~11.3 pF

...

0x12 value ~20.3 pF (default)

...

0x2F: maximum capacitor value ~33.4 pF

Others: reserved

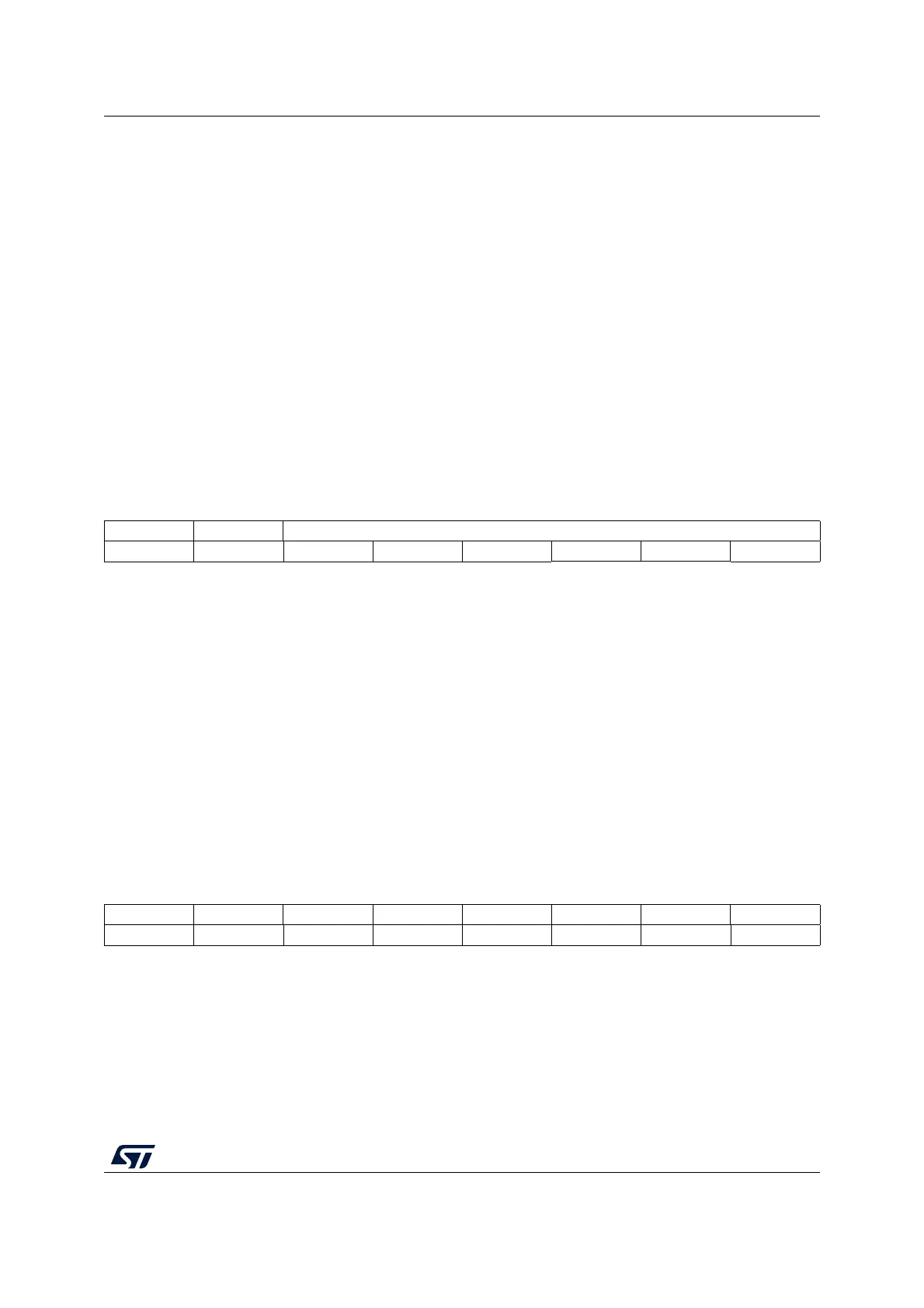

76543210

Res. CLKDE Res. Res. Res. Res. Res. Res.

rw

Bit 7 Reserved, must be kept at reset value.

Bit 6 CLKDE: SMPS clock detection enable

SMPS clock detection must be enabled before enabling the SMPS.

0: SMPS clock detection disabled

1: SMPS clock detection enabled

Bits 5:0 Reserved, must be kept at reset value.

Loading...

Loading...