Low-power timer (LPTIM) RM0453

966/1461 RM0453 Rev 1

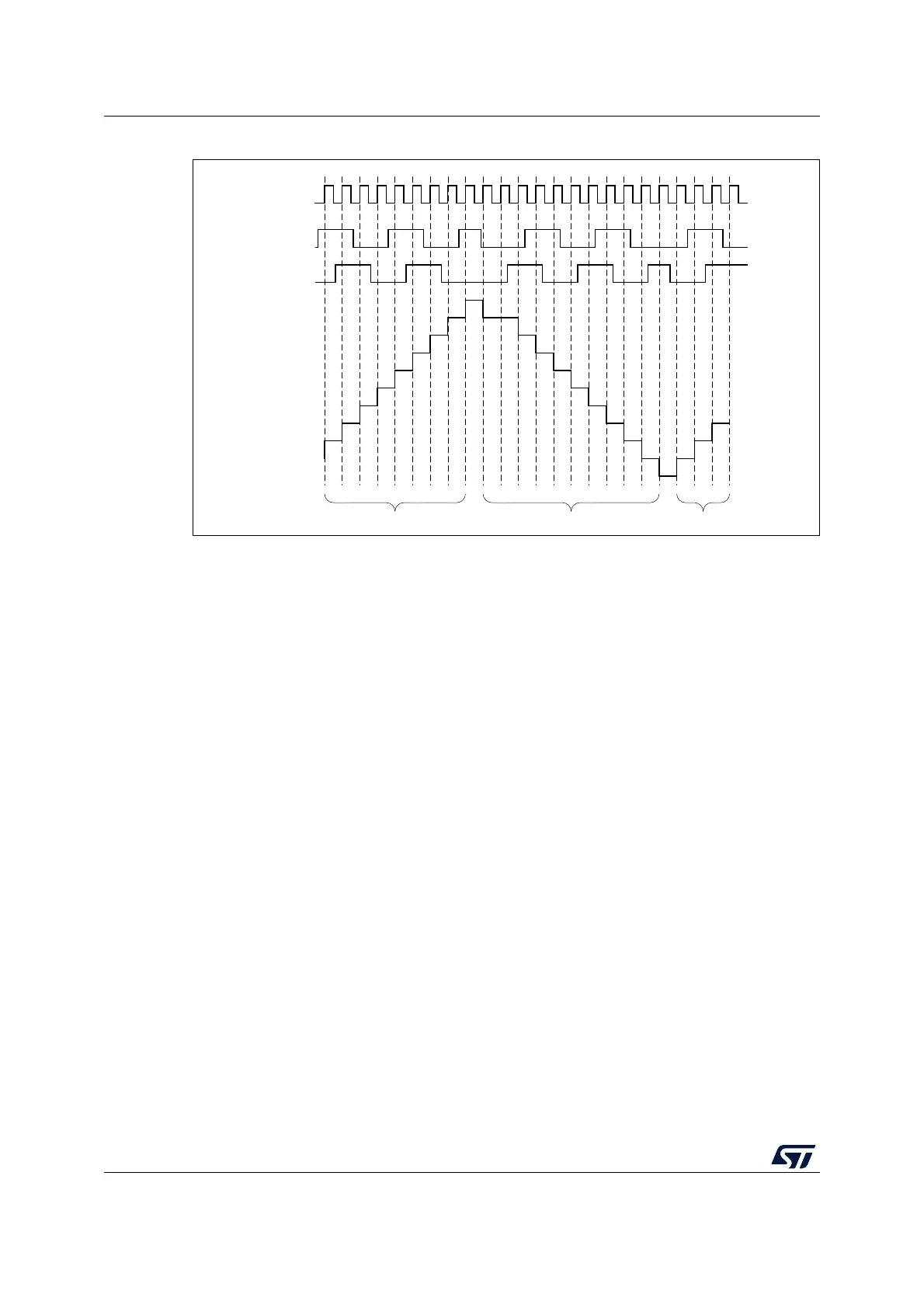

Figure 267. Encoder mode counting sequence

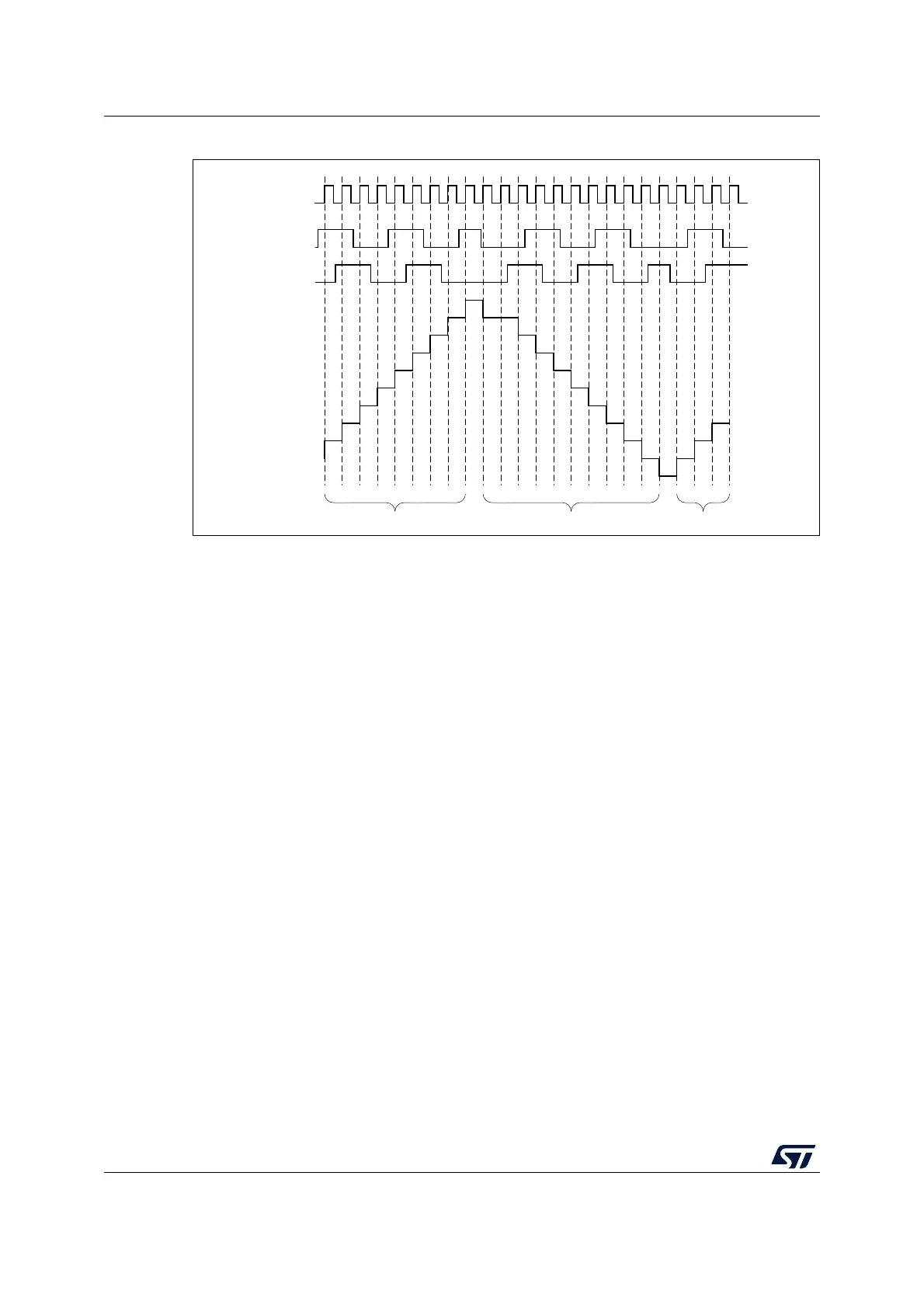

28.4.16 Repetition Counter

The LPTIM features a repetition counter that decrements by 1 each time an LPTIM counter

overflow event occurs. A repetition counter underflow event is generated when the repetition

counter contains zero and the LPTIM counter overflows. Next to each repetition counter

underflow event, the repetition counter gets loaded with the content of the REP[7:0] bit-field

which belongs to the repetition register LPTIM_RCR.

A repetition underflow event is generated on each and every LPTIM counter overflow when

the REP[7:0] register is set to 0.

When PRELOAD = 1, writing to the REP[7:0] bit-field has no effect on the content of the

repetition counter until the next repetition underflow event occurs. The repetition counter

continues to decrement each LPTIM counter overflow event and only when a repetition

underflow event is generated, the new value written into REP[7:0] is loaded into the

repetition counter. This behavior is depicted in Figure 268.

MS32491V1

T1

Counter

up updown

T2

Loading...

Loading...