RM0453 Rev 1 503/1461

RM0453 Nested vectored interrupt controller (NVIC)

505

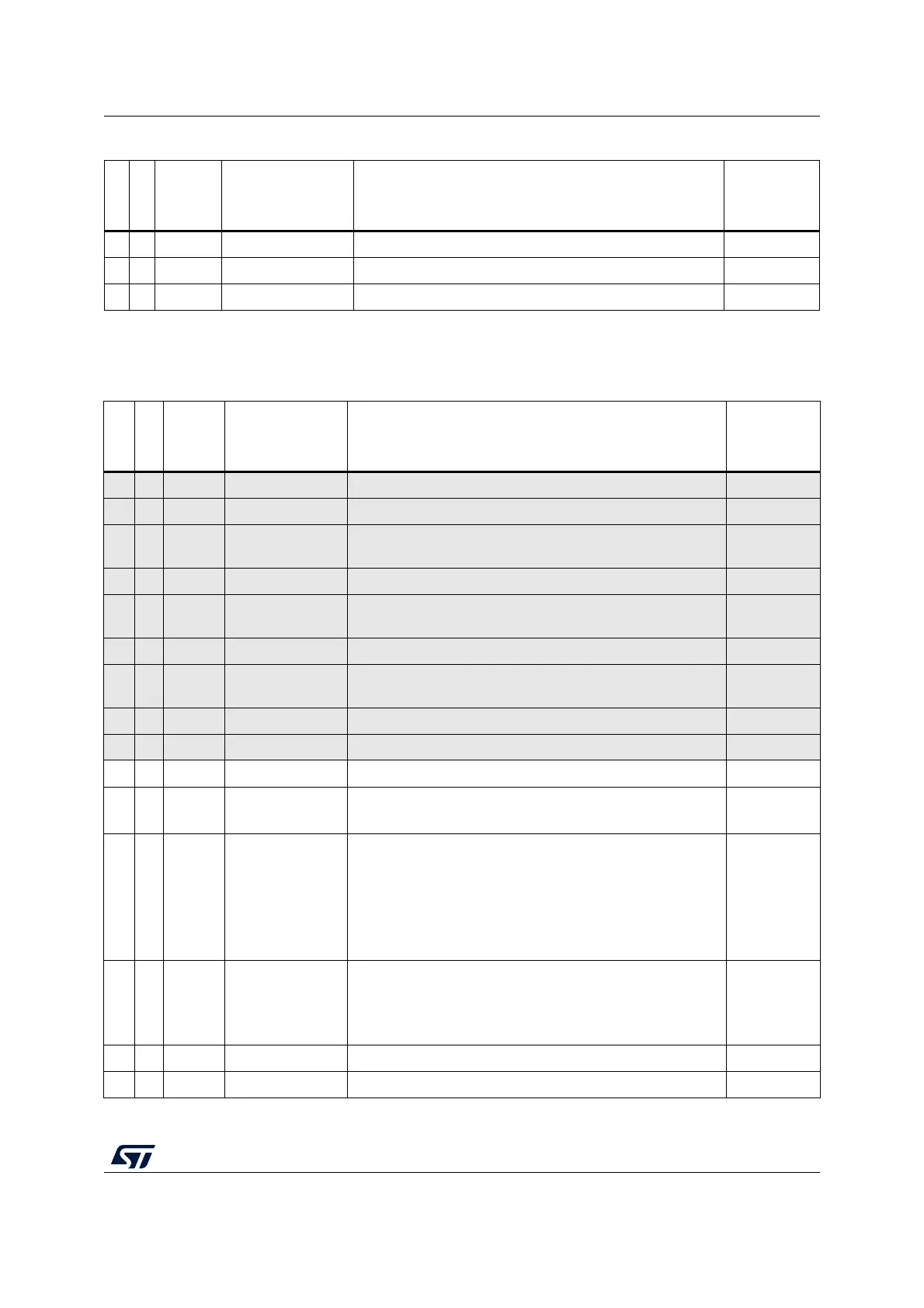

59 66 Settable DMA2_CH6 DMA2 channel 6 non-secure interrupt 0x0000 012C

60 67 Settable DMA2_CH7 DMA2 channel 7 non-secure interrupt 0x0000 0130

61 68 Settable DMAMUX1_OVR DMAMUX1 overrun interrupt 0x0000 0134

1. IMRx[n] refer to the pre-mask bit[n] in SYSCFG_IMRx register.

2. EXTI[n] refer to the input event number [n] of the EXTI.

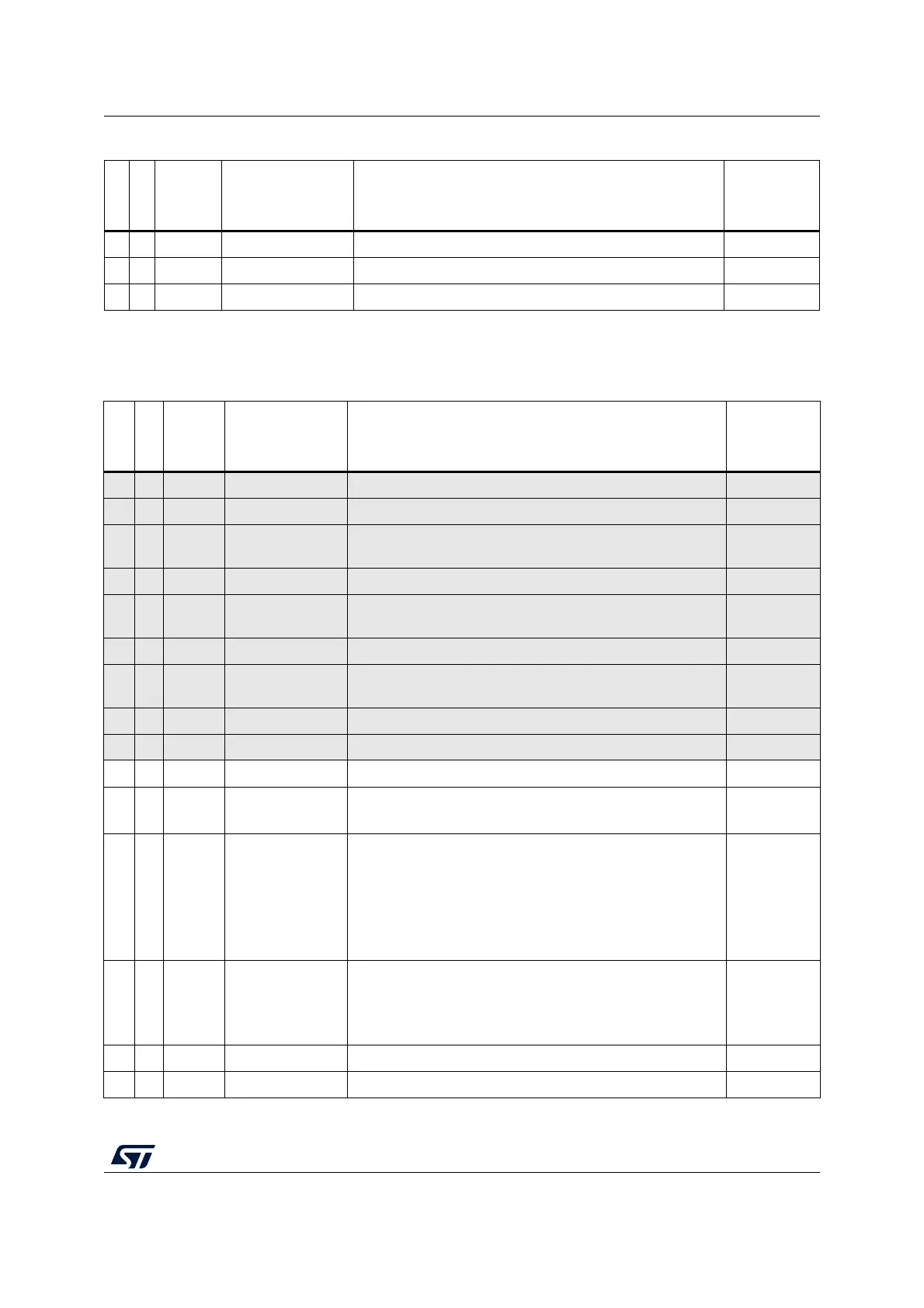

Table 90. CPU2 vector table

Position

Priority

Type of

priority

Acronym Description

(1)(2)

Address

- - - - Reserved 0x0000 0000

- -3 Fixed Reset Reset 0x0000 0004

-14 -2 Fixed NMI

Non maskable interrupt HSE CSS, Flash ECC and SRAM2

parity

0x0000 0008

-13 -1 Fixed HardFault All classes of fault 0x0000 000C

- - - - Reserved

0x0000 0010

0x0000 0028

-5 0 Settable SVCall System service can via SWI instruction 0x0000 002C

- - - - Reserved

0x0000 0030

0x0000 0034

-2 1 Settable PendSV Pendable request for system service 0x0000 0038

-1 2 Settable Systick System tick timer 0x0000 003C

0 3 Settable TZIC_ILA Security Interrupt controller illegal access interrupt 0x0000 0040

1 4 Settable PVD, PVM[3]

PVD through EXTI[16] (C2IMR2[20])

PVM[3] through EXTI[34] (C2IMR2[18])

0x0000 0044

2 5 Settable

TAMP,

RTC_STAMP,

LSE_CSS,

RTC_ALARM,

RTC_SSRU,

RTC_WKUP

TAMP tamper

RTC timestamp

LSECSS interrupt (C2IMR1[0])

RTC alarms A and B interrupt (C2IMR1[1])

RTC SSR underflow interrupt (C2IMR1[2])

RTC wakeup interrupt (C2IMR1[3])

0x0000 0048

3 6 Settable

RCC,

FLASH,

C1SEV

RCC global interrupt (C2IMR1[5])

Flash memory global interrupt and Flash memory ECC

single error interrupt (C2IMR1[6])

CPU1 SEV through EXTI[41]

0x0000 004C

4 7 Settable EXTI[1:0] EXTI line 1:0 interrupt through EXTI[1:0] (C2IMR1[17:16]) 0x0000 0050

5 8 Settable EXTI[3:2] EXTI line 3:2 interrupt through EXTI[3:2] (C2IMR1[19:18]) 0x0000 0054

Table 89. CPU1 vector table (continued)

Position

Priority

Type of

priority

Acronym Description

(1)(2)

Address

Loading...

Loading...