General-purpose I/Os (GPIO) RM0453

394/1461 RM0453 Rev 1

GPIOx_BSRR and GPIOx_BRR registers allow atomic read/modify accesses to any of the

GPIOx_ODR registers. In this way, there is no risk of an IRQ occurring between the read

and the modify access.

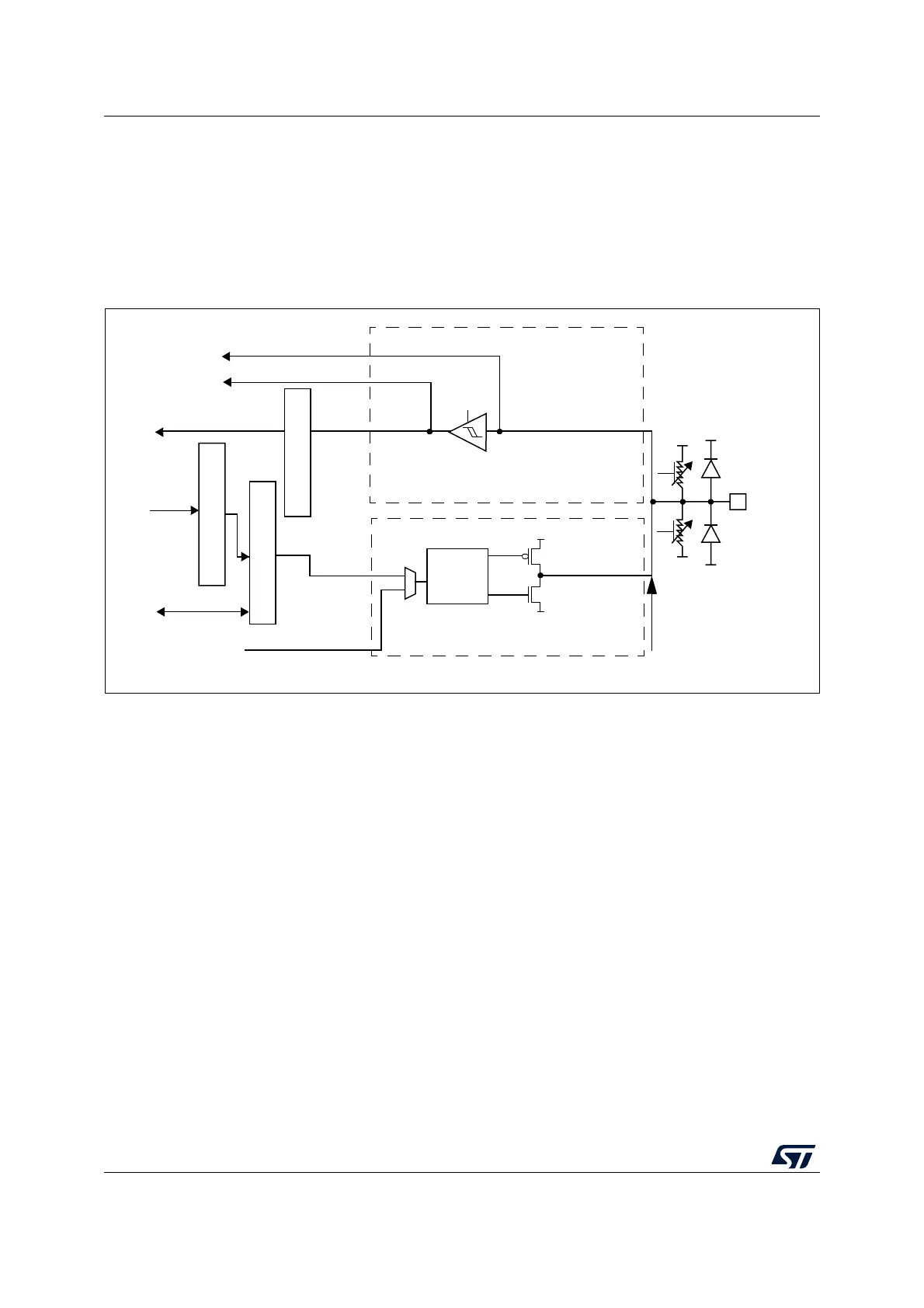

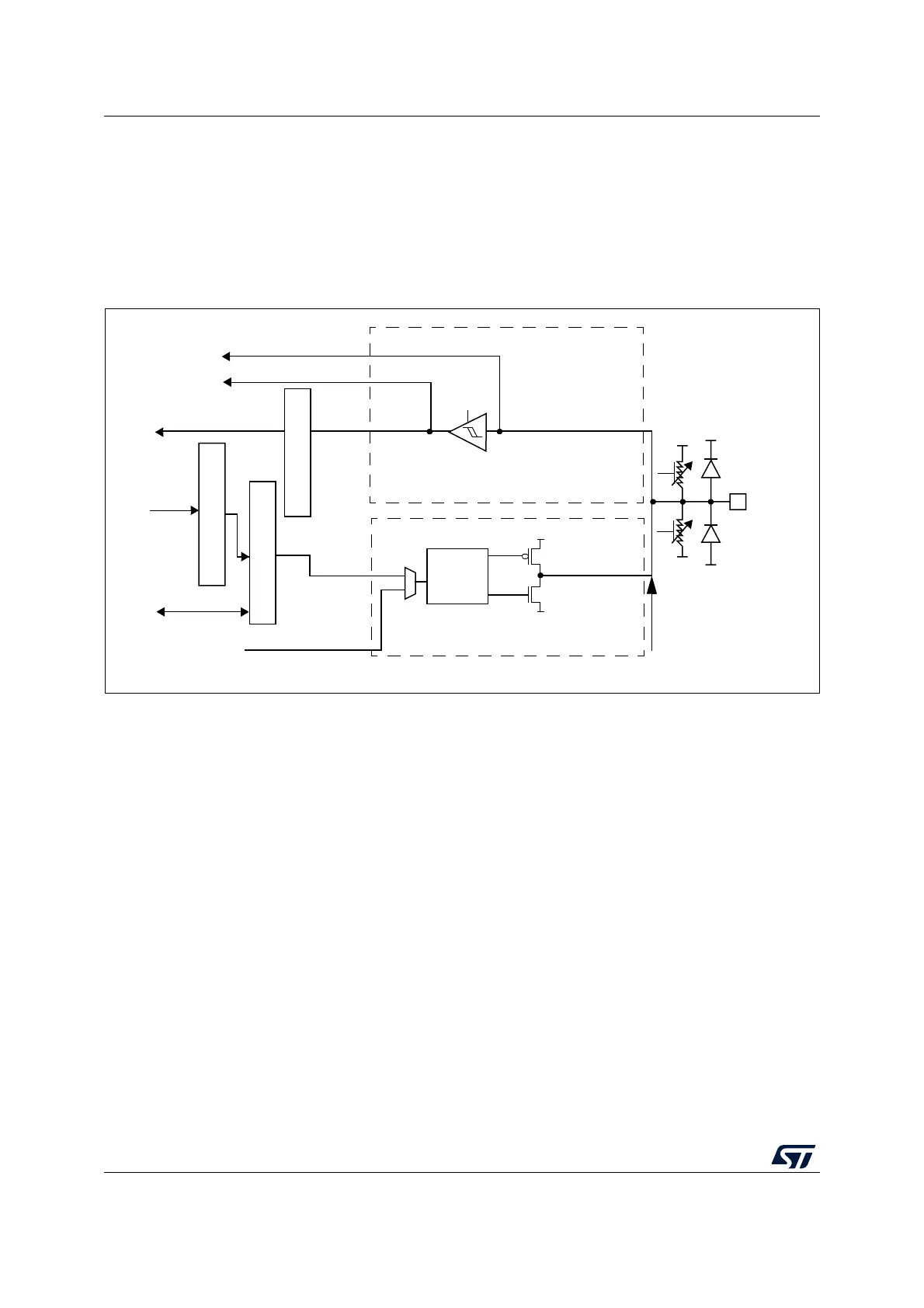

Figure 43 and Figure 44 show the basic structure of a standard and a 5V-tolerant I/O port

bit.

Table 70 gives the possible port bit configurations.

Figure 43. Basic structure of a standard I/O port bit

Alternate function output

Alternate function input

Push-pull,

open-drain or

disabled

Input data register

Output data register

Read/write

From on-chip

peripheral

To on-chip

peripheral

Output

control

Analog

on/off

Pull

Pull

down

on/off

I/O pin

V

DDIOx

V

DDIOx

V

SS

V

SS

trigger

V

SS

V

DDIOx

Protection

diode

Protection

diode

on/off

Input driver

Output driver

up

P-MOS

N-MOS

Read

Bit set/reset registers

Write

Analog

MS31476V1

Loading...

Loading...