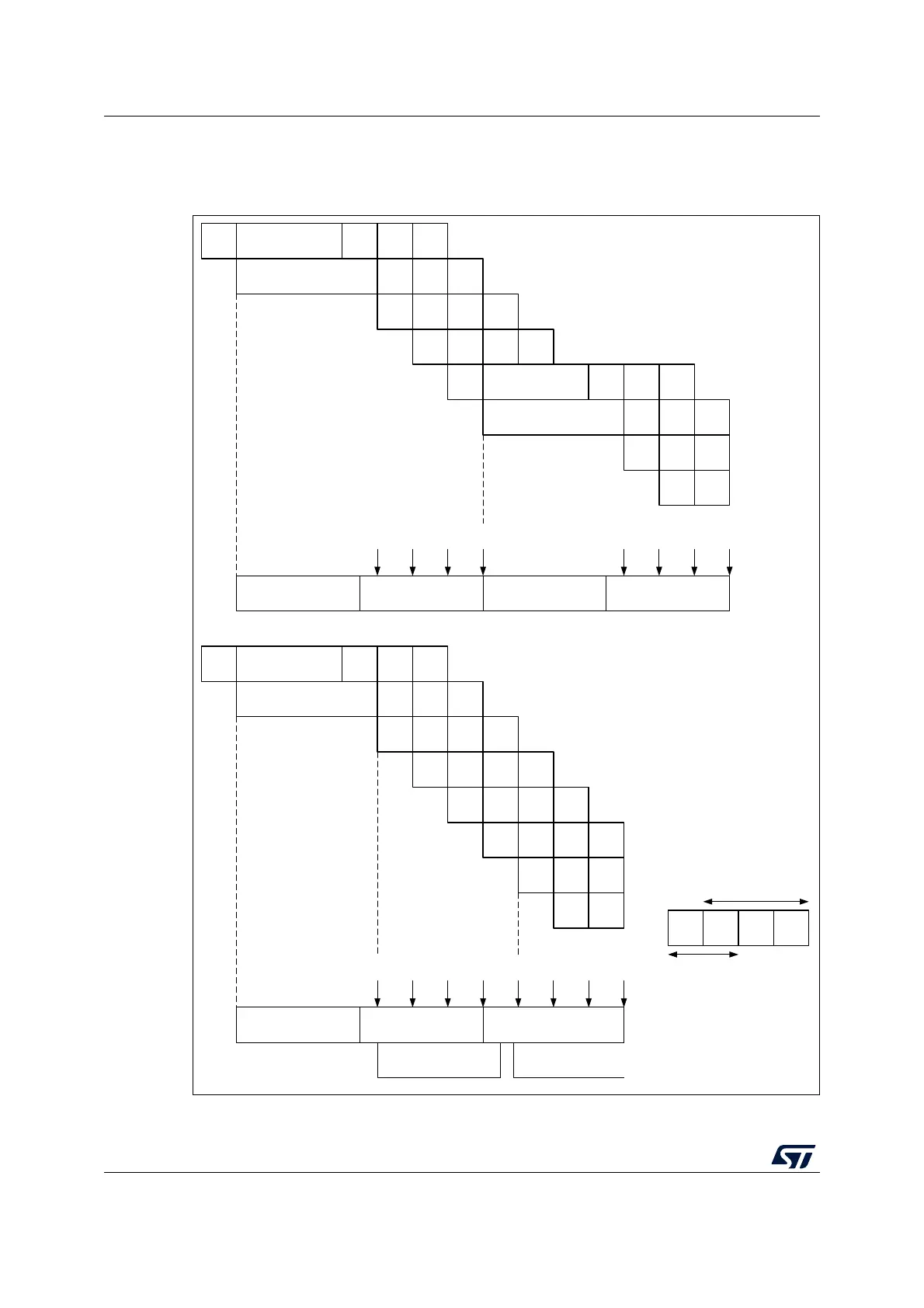

Figure 7. Sequential 16 bits instructions execution

MS33467V1

WITHOUT PREFETCH

@

1

F

1

WAIT

D

1

E

1

@

2

F

2

D

2

E

2

@

3

D

3

E

3

F

3

@

4

D

4

E

4

F

4

@

5

D

5

E

5

F

5

WAIT

D

6

E

6

F

6

@

6

F

7

D

7

@

7

F

8

@

8

Read ins 1, 2, 3, 4 Gives ins 1, 2, 3, 4

ins 1

fetch

ins 2

fetch

ins 3

fetch

ins 4

fetch

Read ins 5, 6, 7, 8 Gives ins 5, 6, 7, 8

ins 5

fetch

ins 6

fetch

ins 7

fetch

ins 8

fetch

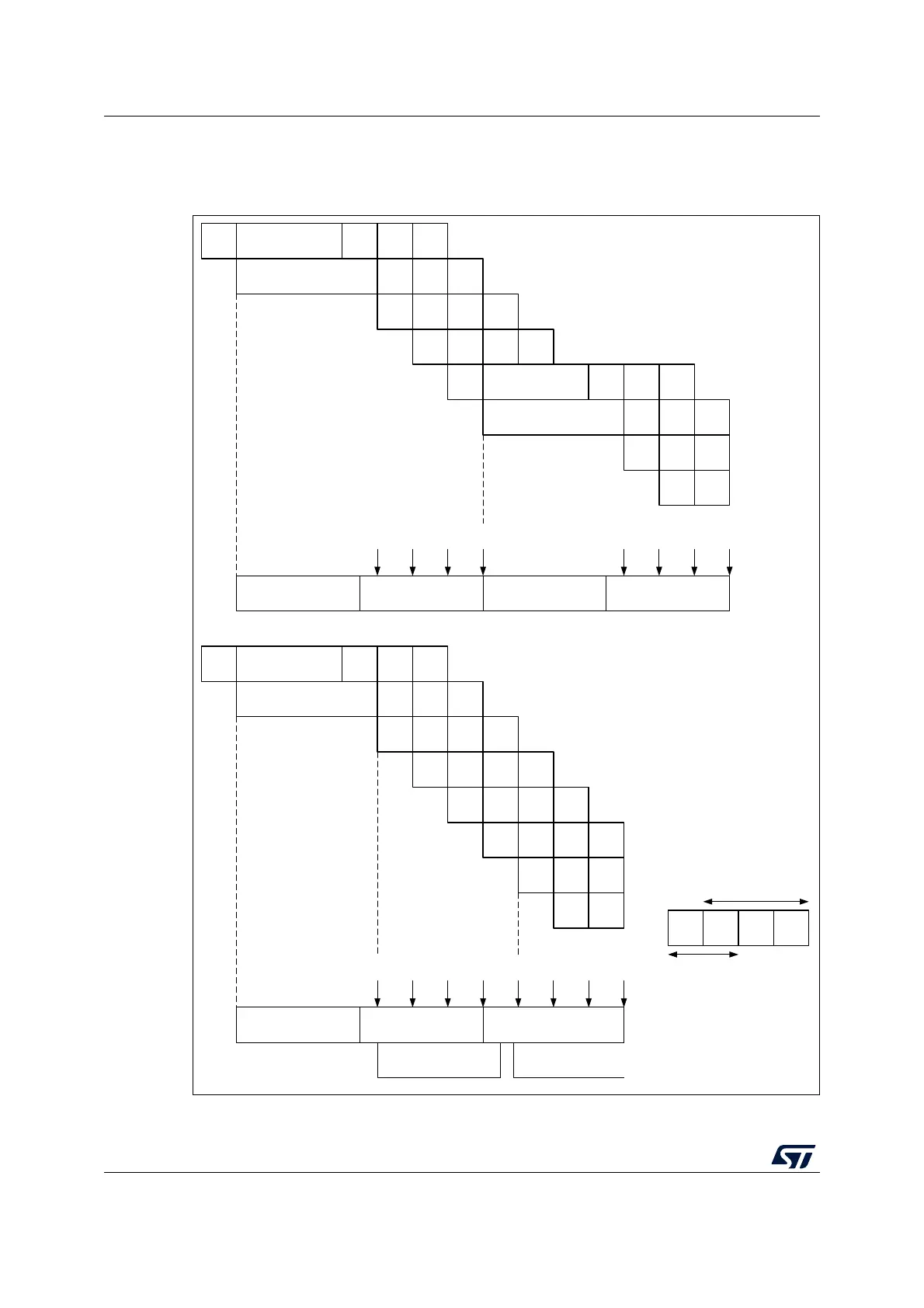

WITH PREFETCH

@

1

F

1

WAIT

D

1

E

1

@

2

F

2

D

2

E

2

@

3

D

3

E

3

F

3

@

4

D

4

E

4

F

4

@

5

D

5

E

5

F

5

D

6

E

6

F

6

F

7

D

7

@

7

F

8

@

8

Read ins 1, 2, 3, 4 Gives ins 1, 2, 3, 4

ins 1

fetch

ins 2

fetch

ins 3

fetch

ins 4

fetch

Gives ins 5, 6, 7, 8

ins 5

fetch

ins 6

fetch

ins 7

fetch

ins 8

fetch

@

6

Read ins 5, 6, 7, 8 Read ins 9, 10, ...

@: address requested

F: Fetch stage

D: Decode stage

E: Execute stage

D

6

E

6

F

6

@

6

Cortex-M4 pipeline

AHB protocol

Loading...

Loading...