Tamper and backup registers (TAMP) RM0453

1050/1461 RM0453 Rev 1

33.6.4 TAMP filter control register (TAMP_FLTCR)

Address offset: 0x0C

Backup domain reset value: 0x0000 0000

System reset: not affected

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 ITAMP8NOER: Internal Tamper 8 no erase

0: Internal Tamper 8 event erases the backup registers.

1: Internal Tamper 8 event does not erase the backup registers

(1)

.

Bit 6 Reserved, must be kept at reset value.

Bit 5 ITAMP6NOER: Internal Tamper 6 no erase

0: Internal Tamper 6 event erases the backup registers.

1: Internal Tamper 6 event does not erase the backup registers

(1)

.

Bit 4 ITAMP5NOER: Internal Tamper 5 no erase

0: Internal Tamper 5 event erases the backup registers.

1: Internal Tamper 5 event does not erase the backup registers

(1)

.

Bit 3 Reserved, must be kept at reset value.

Bit 2 ITAMP3NOER: Internal Tamper 3 no erase

0: Internal Tamper 3 event erases the backup registers.

1: Internal Tamper 3 event does not erase the backup registers

(1)

.

Bit 1 Reserved, must be kept at reset value.

Bit 0 Reserved, must be kept at reset value.

1. and the device secrets erased by tamp_erase signal (refer to Table 218: TAMP interconnection).

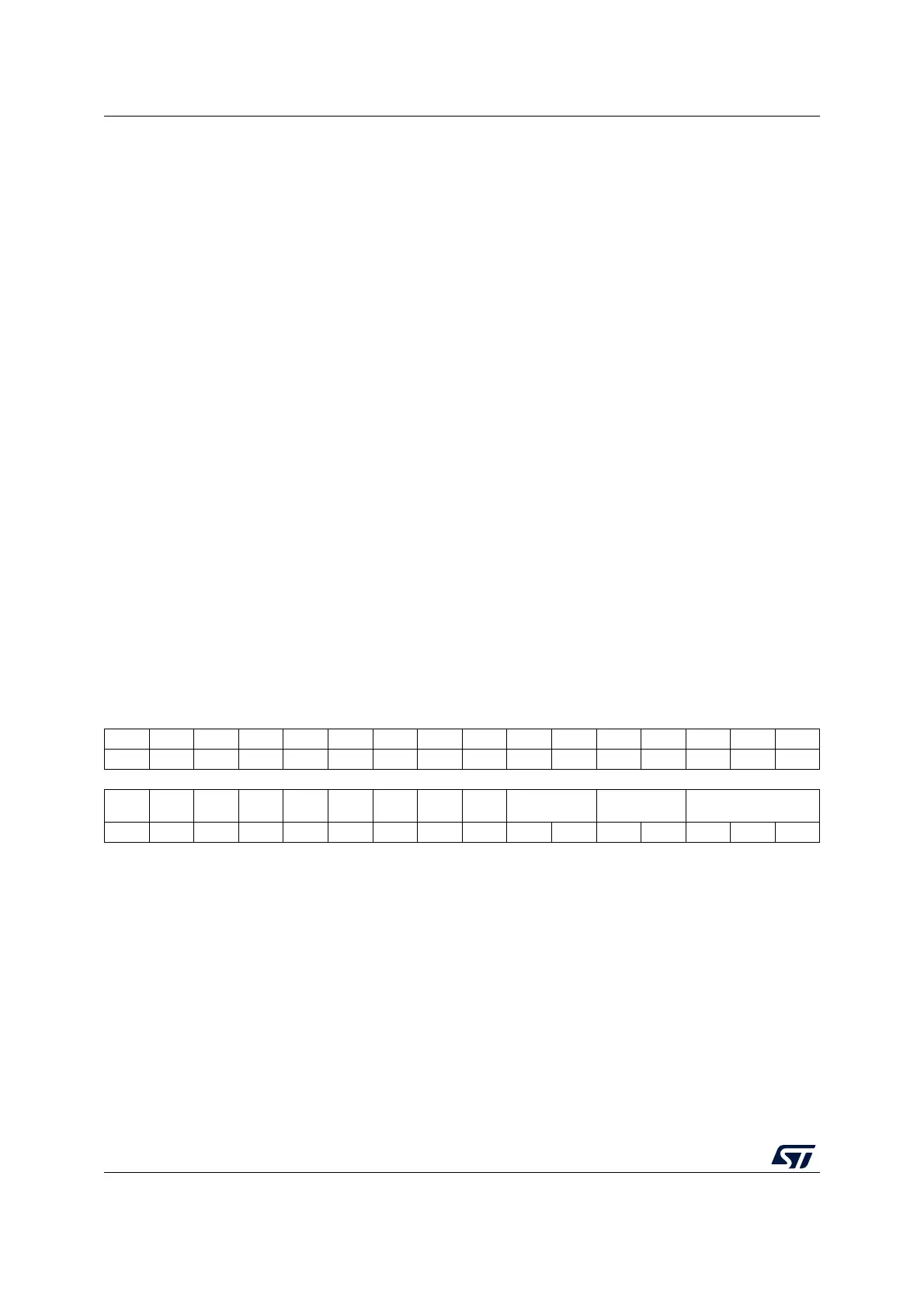

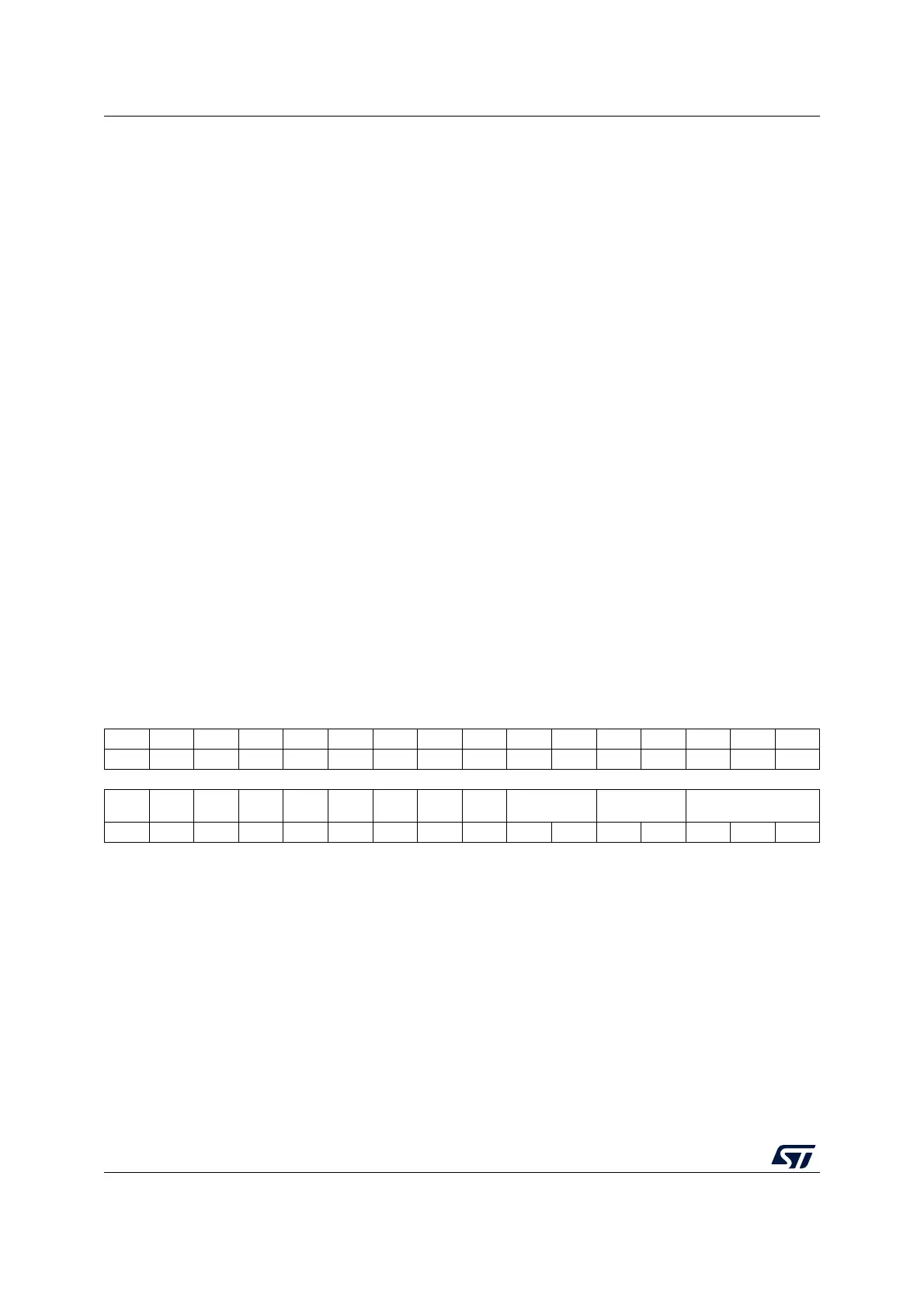

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res.

TAMP

PUDIS

TAMPPRCH

[1:0]

TAMPFLT

[1:0]

TAMPFREQ

[2:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 TAMPPUDIS: TAMP_INx pull-up disable

This bit determines if each of the TAMPx pins are precharged before each sample.

0: Precharge TAMP_INx pins before sampling (enable internal pull-up)

1: Disable precharge of TAMP_INx pins.

Loading...

Loading...