Low-power universal asynchronous receiver transmitter (LPUART) RM0453

1216/1461 RM0453 Rev 1

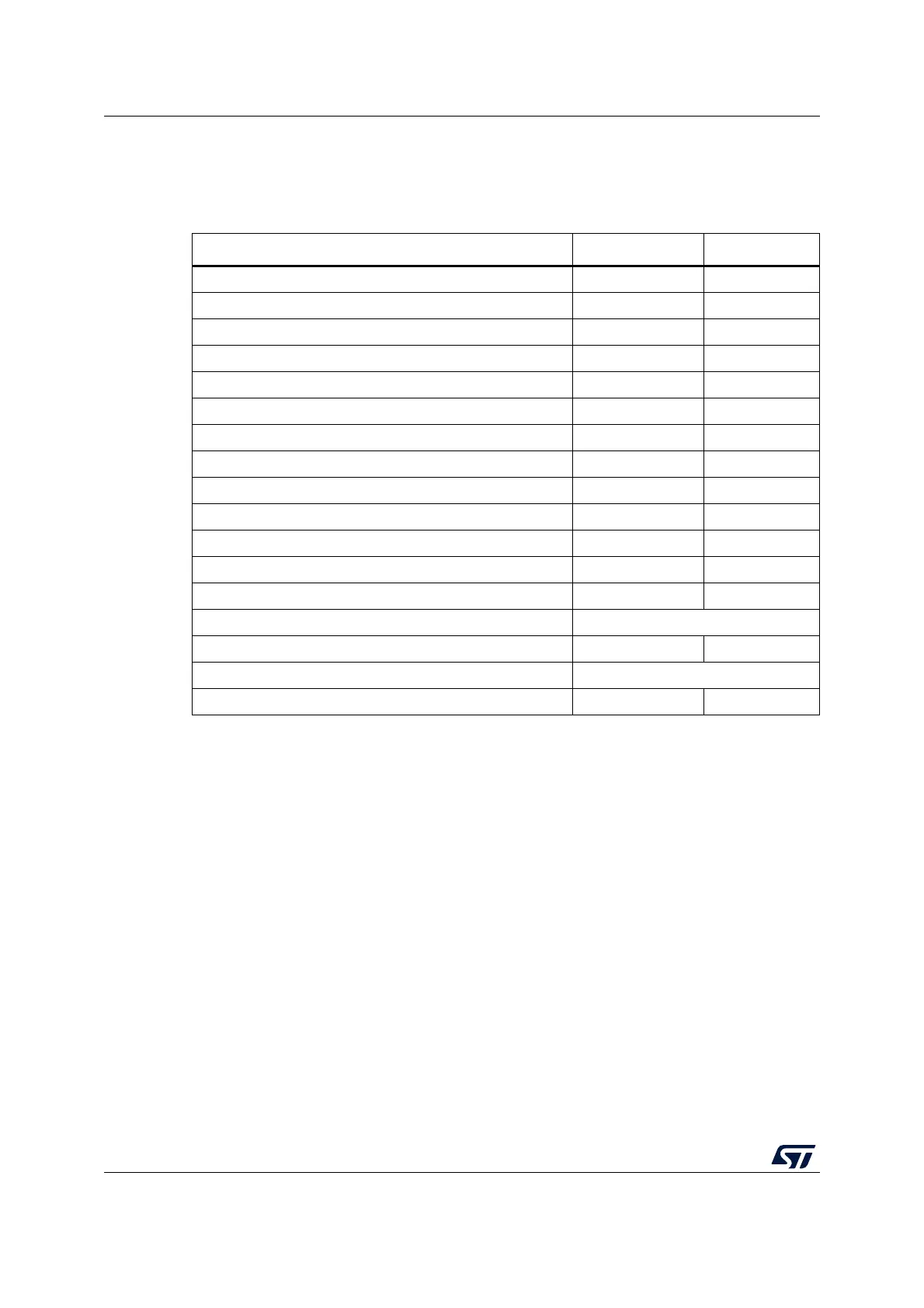

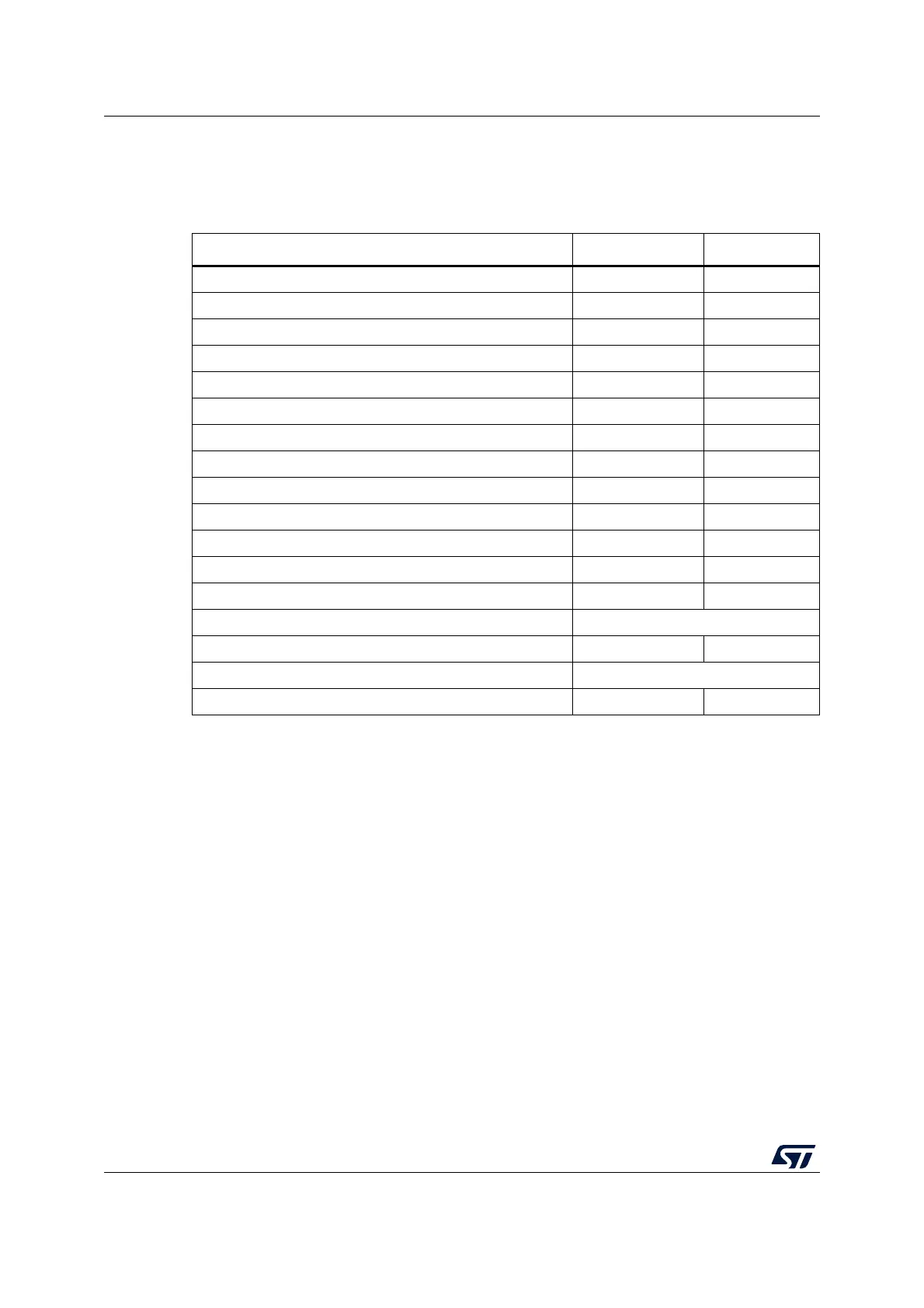

36.3 LPUART implementation

Below the description of LPUART implementation in comparison with USART.

Table 247. USART / LPUART features

USART /LPUART modes/features

(1)

1. X = supported.

USART1/2 LPUART1

Hardware flow control for modem X X

Continuous communication using DMA X X

Multiprocessor communication X X

Synchronous mode (Master/Slave) X -

Smartcard mode X -

Single-wire Half-duplex communication X X

IrDA SIR ENDEC block X -

LIN mode X -

Dual clock domain and wakeup from low-power mode X X

Receiver timeout interrupt X -

Modbus communication X -

Auto baud rate detection X -

Driver Enable X X

USART data length 7, 8 and 9 bits

Tx/Rx FIFO X X

Tx/Rx FIFO size 8

Wakeup from Stop mode X

(2)

2. Wakeup supported from Stop 0 and Stop 1 modes.

X

(3)

3. Wakeup supported from Stop 0, Stop 1 and Stop 2 modes.

Loading...

Loading...