RM0453 Rev 1 727/1461

RM0453 Public key accelerator (PKA)

728

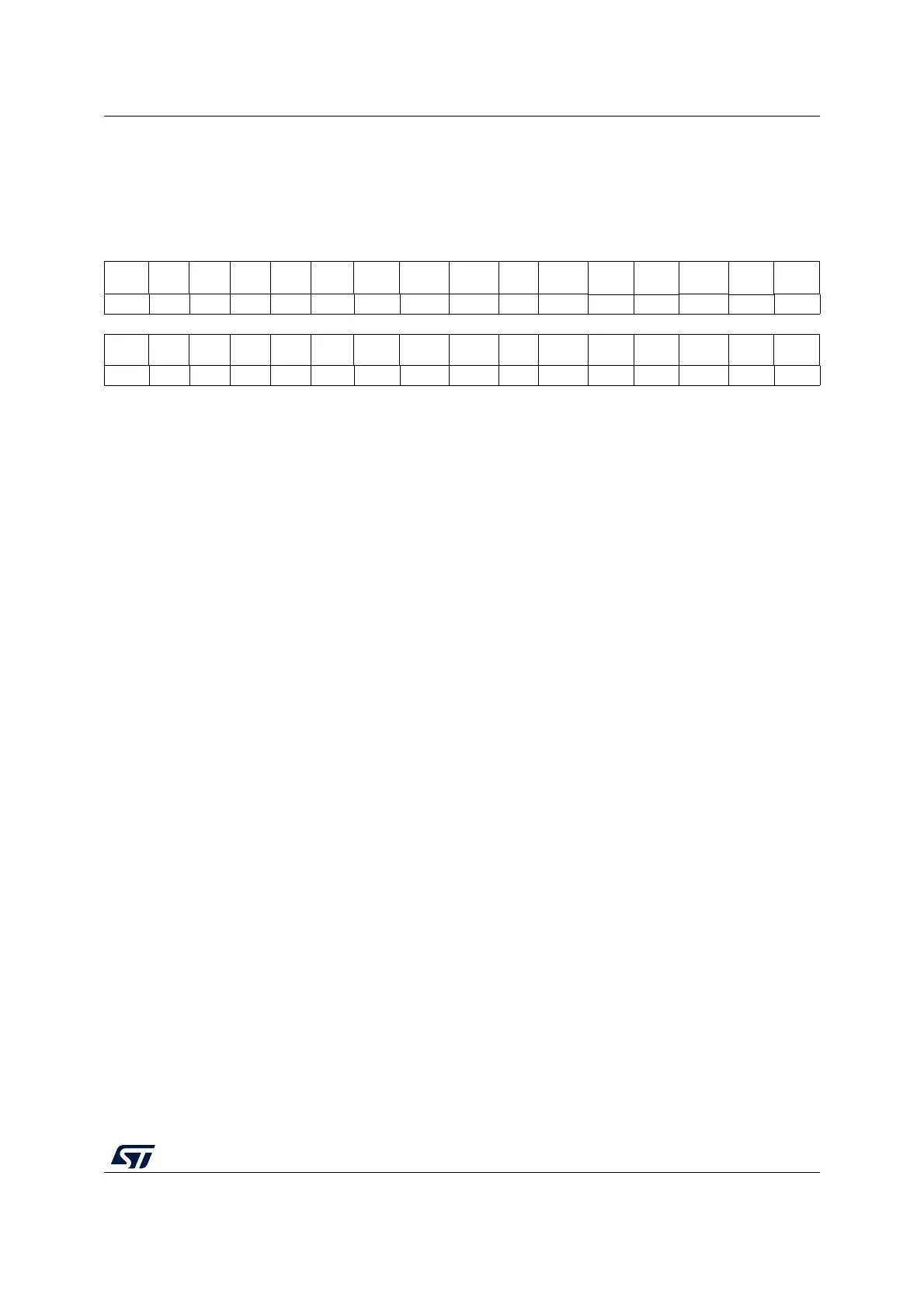

24.7.3 PKA clear flag register (PKA_CLRFR)

Address offset: 0x08

Reset value: 0x0000 0000

Note: Reading PKA_CLRFR returns all 0s.

24.7.4 PKA RAM

The PKA RAM is mapped at the offset address of 0x0400 compared to the PKA base

address. Only 32-bit word single accesses are supported, through PKA.AHB interface.

RAM size is 3576 bytes (max word offset: 0x11F4).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ADDR

ERRFC

RAM

ERRFC

Res.

PROC

ENDFC

Res.

ww w

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

Bits 31:21 Reserved, must be kept at reset value.

Bit 20 ADDRERRFC: Clear Address error flag

0: No action

1: Clear the ADDRERRF flag in PKA_SR

Bit 19 RAMERRFC: Clear PKA RAM error flag

0: No action

1: Clear the RAMERRF flag in PKA_SR

Bit 18 Reserved, must be kept at reset value.

Bit 17 PROCENDFC: Clear PKA End of Operation flag

0: No action

1: Clear the PROCENDF flag in PKA_SR

Bits 16:0 Reserved, must be kept at reset value.

Loading...

Loading...