System window watchdog (WWDG) RM0453

994/1461 RM0453 Rev 1

Note: The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is

cleared).

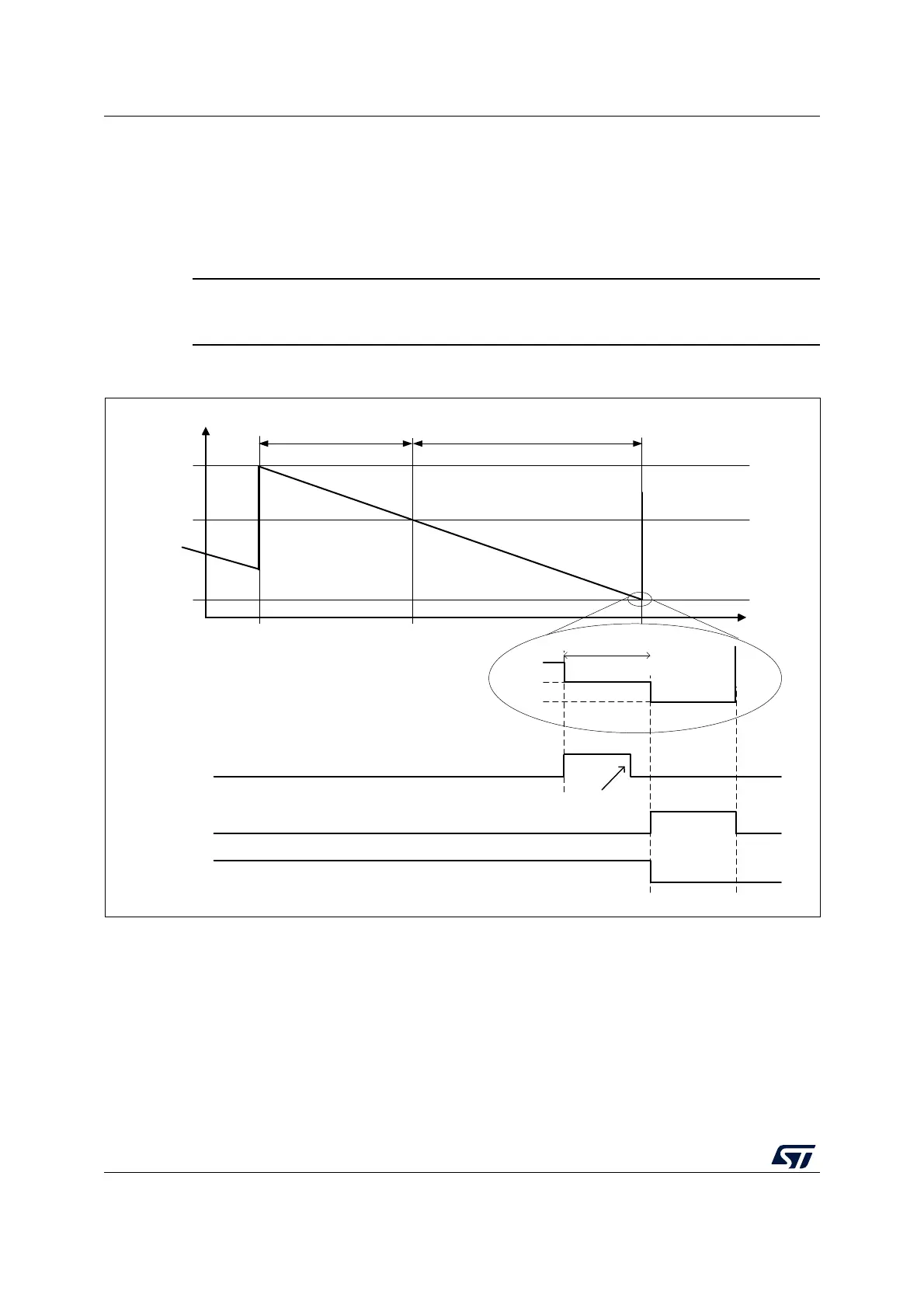

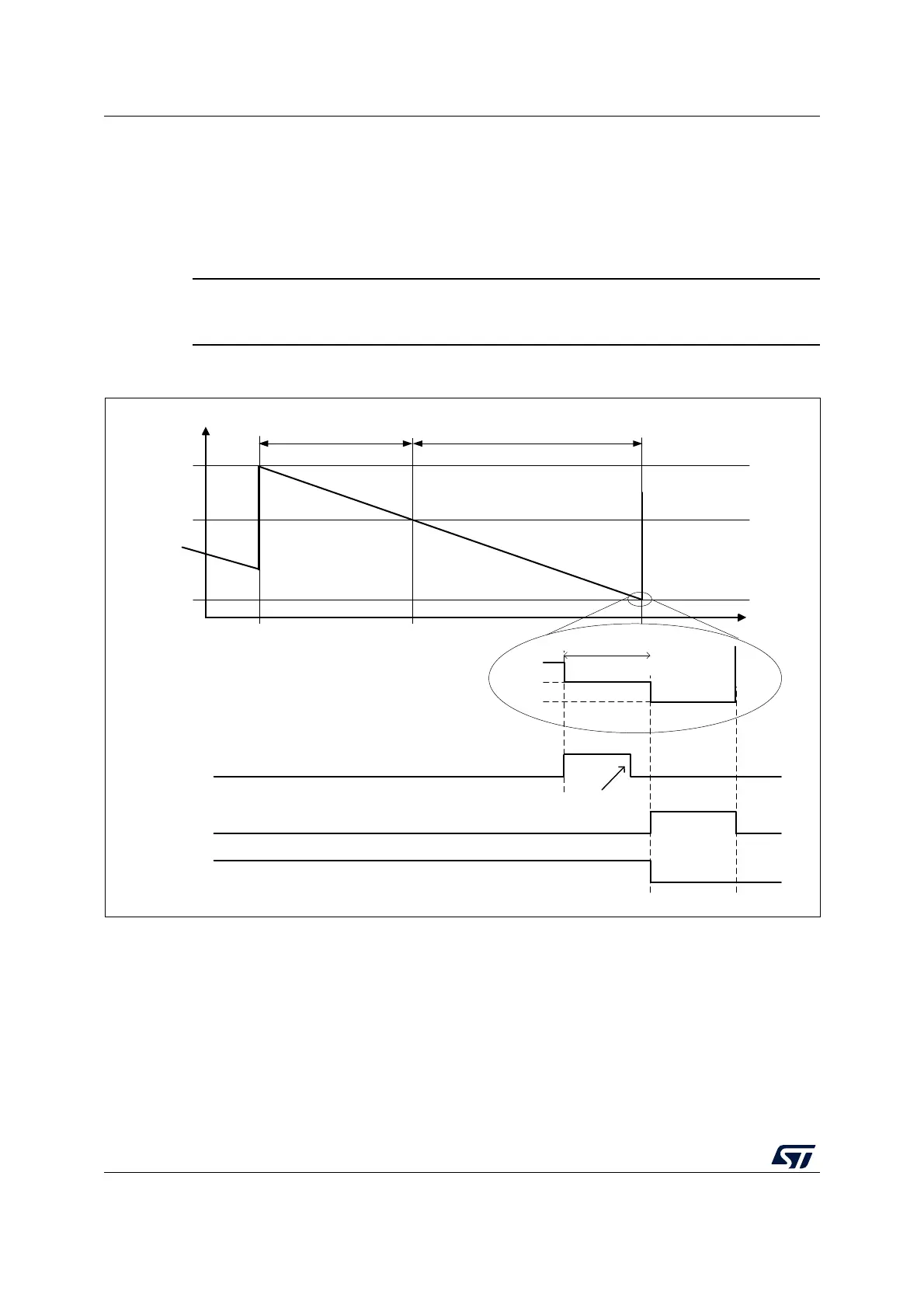

31.3.5 How to program the watchdog timeout

Use the formula in Figure 272 to calculate the WWDG timeout.

Warning: When writing to the WWDG_CR register, always write 1 in the

T6 bit to avoid generating an immediate reset.

Figure 272. Window watchdog timing diagram

The formula to calculate the timeout value is given by:

where:

t

WWDG

: WWDG timeout

t

PCLK

: APB clock period measured in ms

4096: value corresponding to internal divider

MS47266V1

W[6:0]

0x3F

0x41

0x40

0x3F

wwdg_ewit

wwdg_rst

Refresh not allowed Refresh allowed

Time

T[6:0]

T

pclk

x 4096 x 2

WDGTB

CNT DownCounter

T6 bit

EWIF = 0

t

WWDG

t

PCLK

4096 2

WDGTB[2:0]

T5:0[]1+()×××=ms()

Loading...

Loading...