RM0453 Rev 1 1341/1461

RM0453 Debug support (DBG)

1448

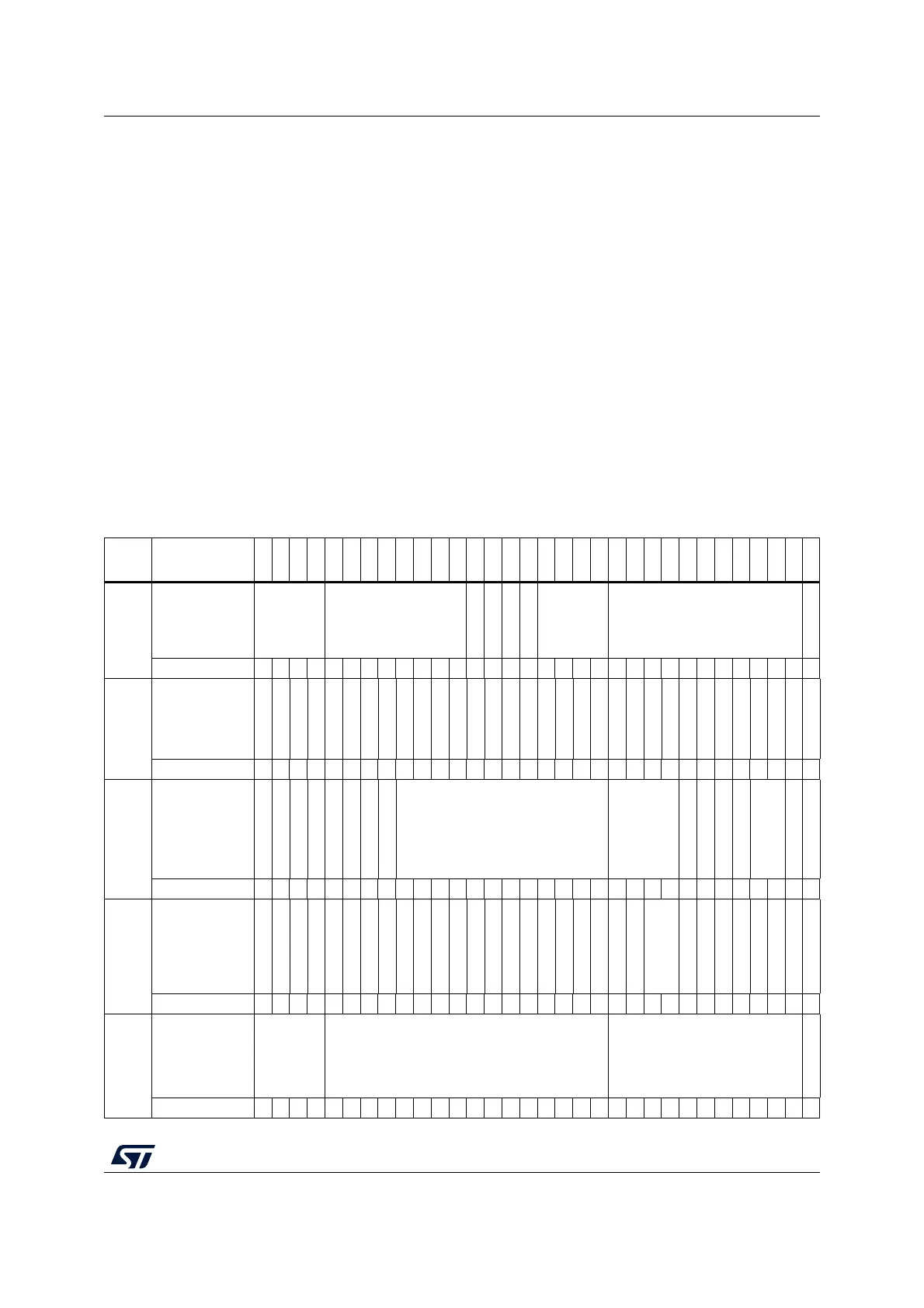

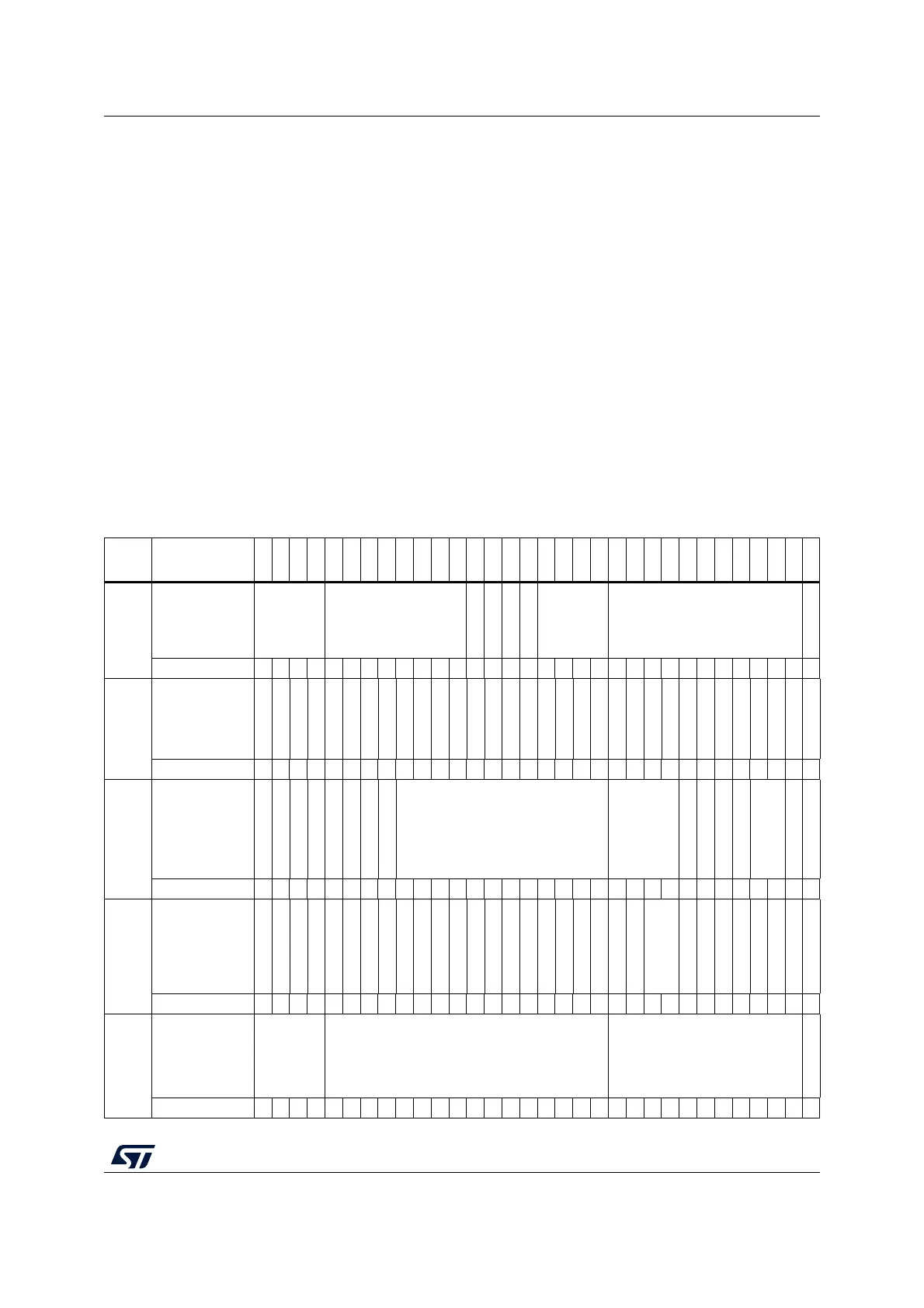

38.4.11 DP register map and reset values

These registers are not on the CPU memory bus and are only accessed through SW-DP

and JTAG-DP debug interface.

The debug port address is 2-bit wide, defined in the JTAG-DP register DPACC or SW-DP

packet request A[3:2] field.

Bits 31:28 TINSTANCE[3:0]: target instance number

Defines the instance number for the target device in a multi-drop system. These bits must be

written with the same value used for DP_DLPIDR.TINSTANCE to select this device.

Bits 27:12 TPARTNO[15:0]: target part number

Defines the part number for the target device. These bits must be written with the same value

used for DP_TARGETIDR.TPARTNO to select this device.

Bits 11:1 TDESIGNER[10:0]: target designer JEDEC code

Defines the JEDEC code for the target device. These bits must be written with the same

value used for DP_TARGETIDR.TDESIGNER to select this device.

Bit 0 Reserved, must be kept at reset value.

Table 268. DP register map and reset values

Offset Register name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

DP_DPIDR

REVISION[3:0]

PARTNO[7:0]

Res.

Res.

Res.

MIN

VERSION[3:0]

DESIGNER[10:0]

Res.

Reset value 010110111010 0001001000111011

0x00

DP_ABORTR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

ORUNERRCLR

WDERRCLR

STKERRCLR

STKCMPCLR

DAPABORT

Reset value 00000

0x04

(1)

DP_CTRLSTATR

Res.

Res.

CDBGPWRUPACK

CDBGPWRUPREQ

Res.

Res.

Res.

Res.

TRNCNT[11:0]

MASKLANE[3:0]

WDATAERR

READOK

STICKYERR

STICKYCMP

TRNMODE[1:0]

STICKYORUN

ORUNDETECT

Reset value 00 000000000000000000000000

0x04

(2)

DP_DLCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

TURNROUND[1:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Reset value 00

0x04

(3)

DP_TARGETIDR

TREVISION[3:0]

TPARTNO[15:0] TDESIGNER[10:0]

Res.

Reset value 0000010010010111000000000100000

Loading...

Loading...