Debug support (DBG) RM0453

1402/1461 RM0453 Rev 1

38.10.5 ITM CoreSight peripheral identity register 4 (ITM_PIDR4)

Address offset: 0xFD0

Reset value: 0x0000 0004

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 BUSY: Indicates whether the ITM is currently processing events (read only).

0: Not busy

1: Busy

Bits 22:16 TRACEBUSID[6:0]: identifier for multi-source trace stream formatting

If multi-source trace is in use, the debugger must write a non-zero value to this field.

Note: Different IDs must be used for each trace source in the system.

Bits 15:10 Reserved, must be kept at reset value.

Bits 9:8 TSPRESCALE[1:0]: local timestamp prescaler

Used with the trace packet reference clock. The possible values are:

0x0: No prescaling

0x1: Divides by 4.

0x2: Divides by 16.

0x3: Divides by 64.

Bits 7:5 Reserved, must be kept at reset value.

Bit 4 SWOENA: enable for asynchronous clocking of the timestamp counter (read only)

0: Timestamp counter uses processor clock

Bit 3 TXENA: Enables forwarding of hardware event packets from the DWT unit to the trace port.

0: Disabled

1: Enabled

Bit 2 SYNCENA: enable for packet transmission synchronization

Note: The debugger setting this bit must also configure the DWT_CTRLR register SYNCTAP

field in the DWT for the correct synchronization speed.

0: Disabled

1: Enabled

Bit 1 TSENA: enable for local timestamp generation

0: Disabled

1: Enabled

Bit 0 ITMENA: ITM enable

0: Disabled

1: Enabled

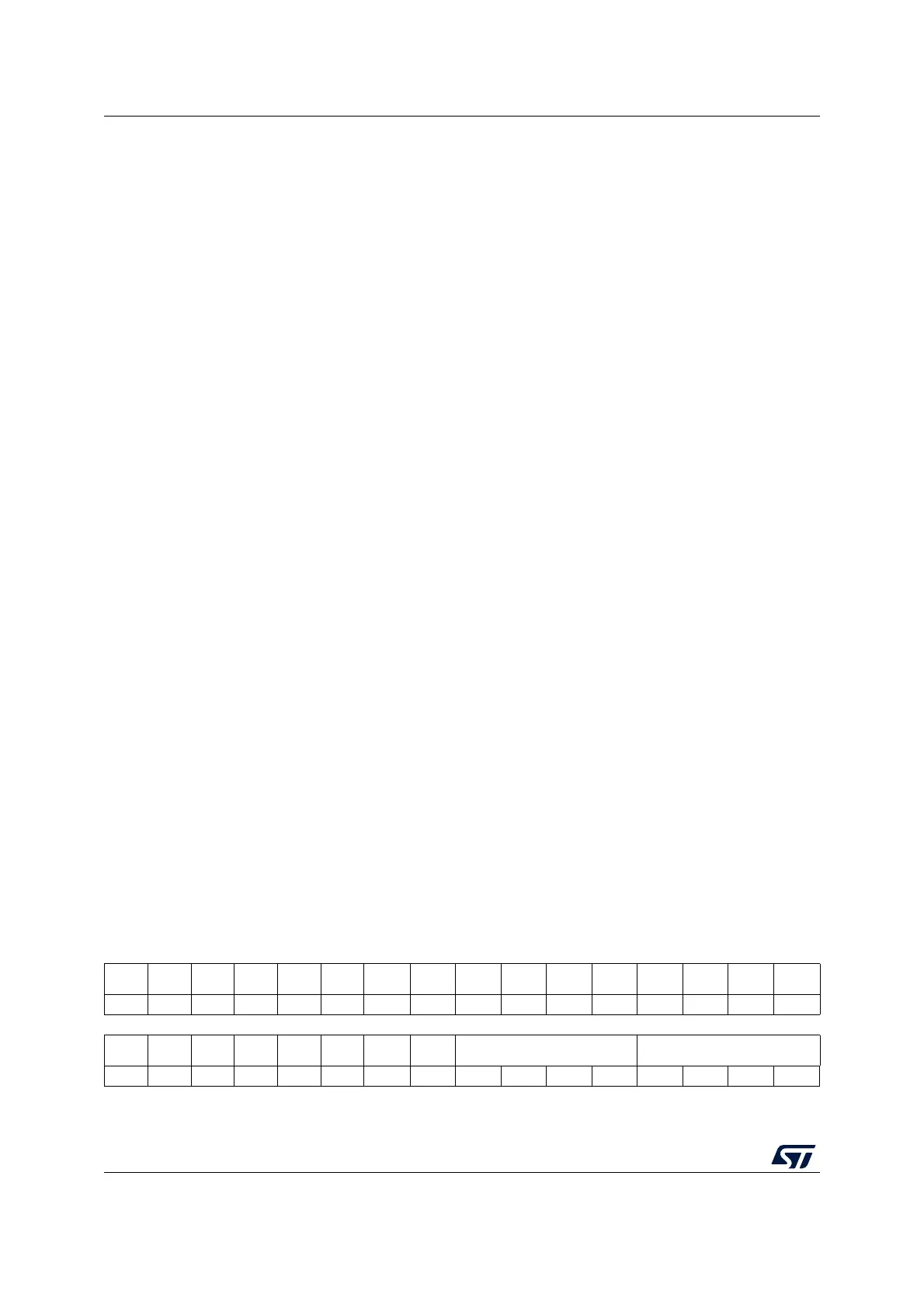

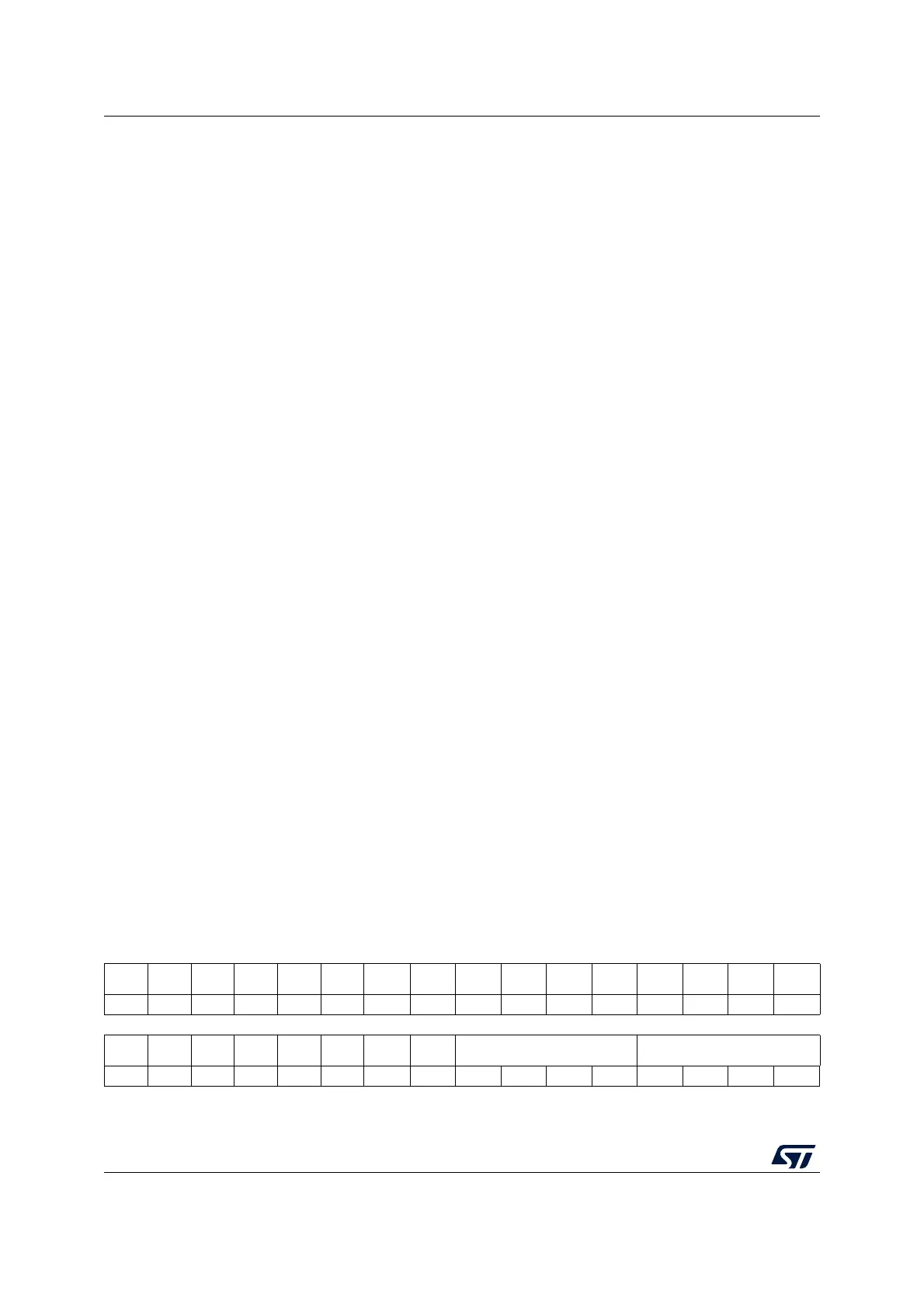

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. F4KCOUNT[3:0] JEP106CON[3:0]

rrrrrrrr

Loading...

Loading...