Sub-GHz radio (SUBGHZ) RM0453

198/1461 RM0453 Rev 1

Cfg_DioIrq() command

Cfg_DioIrq(IrqMask, Irq1Mask, Irq2Mask, Irq3Mask) allows interrupts to be

masked and mapped on the IRQ lines.

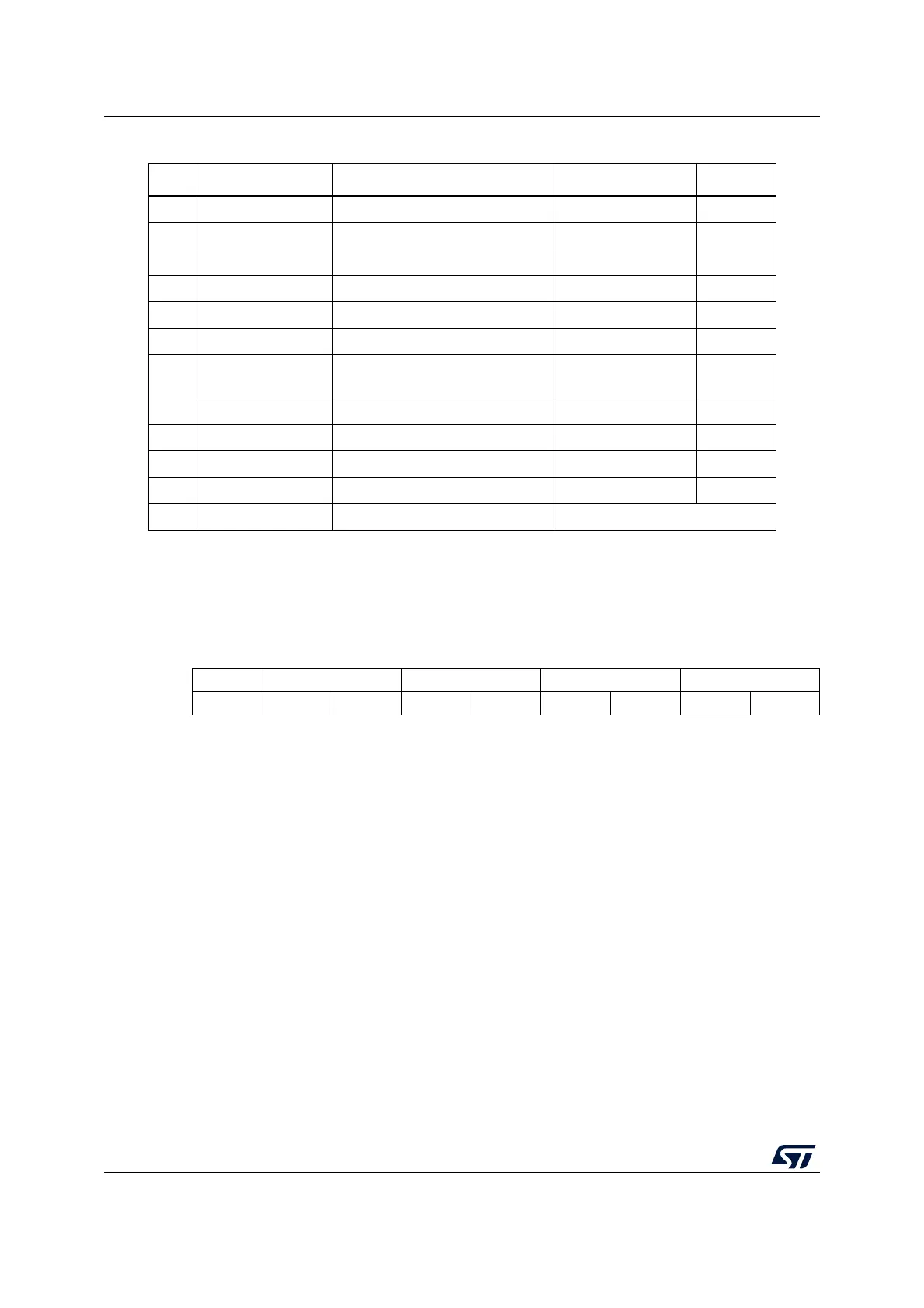

Table 37. IRQ bit mapping and definition

Bit Source Description Packet type Operation

0 TxDone Packet transmission finished LoRa and GFSK Tx

1 RxDone Packet reception finished LoRa and GFSK Rx

2 PreambleDetected Preamble detected LoRa and GFSK Rx

3 SyncDetected Synchronization word valid GFSK Rx

4 HeaderValid Header valid LoRa Rx

5 HeaderErr Header CRC error LoRa Rx

6

Err

preamble, syncword, address,

CRC or length error

GFSK Rx

CrcErr CRC error LoRa Rx

7 CadDone Channel activity detection finished LoRa Cad

8 CadDetected Channel activity detected LoRa Cad

9 Timeout RX or TX timeout LoRa and GFSK Rx and Tx

15:10 Not applicable Reserved Not applicable

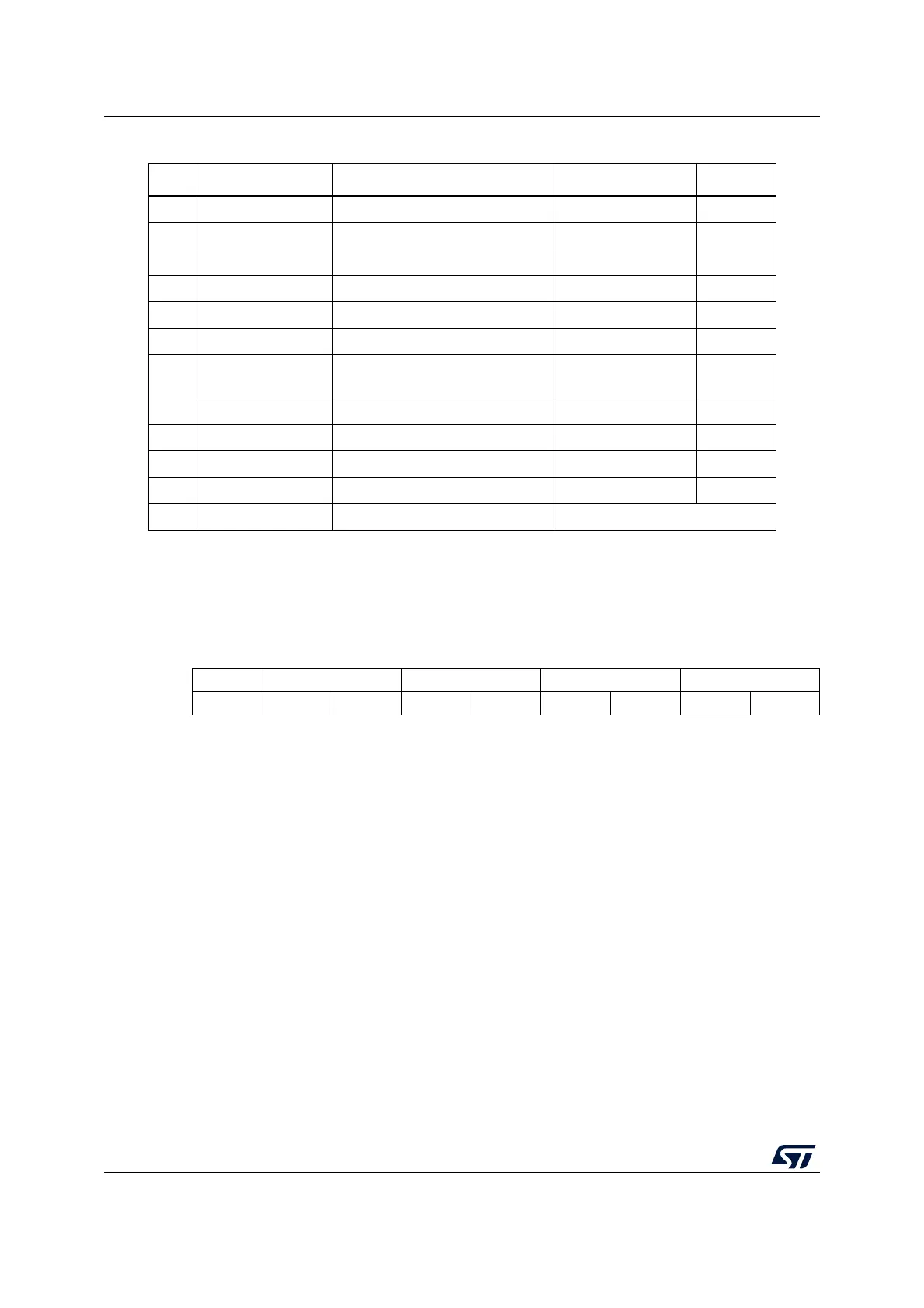

012345678

Opcode IrqMask[15:0] Irq1Mask[15:0]Irq2Mask[15:0]Irq3Mask[15:0]

wwwwwwwww

byte 0 bits 7:0 Opcode: 0x08

bytes 2:1 bits 15:0 IrqMask[15:0]: Global interrupt enable

See Table 37 for interrupt bit map definition. For each bit:

0: IRQ disabled

1: IRQ enabled

bytes 4:3 bits 15:0 Irq1Mask[15:0]: IRQ1 line Interrupt enable

0: interrupt on IRQ1 line disable

1: interrupt on IRQ1 line enabled

bytes 6:5 bits 15:0 Irq2Mask[15:0]: IRQ2 line Interrupt enable

0: interrupt on IRQ2 line disable

1: interrupt on IRQ2 line enabled

bytes 8:7 bits 15:0 Irq3Mask[15:0]: IRQ3 line Interrupt enable

0: interrupt on IRQ3 line disable

1: interrupt on IRQ3 line enabled

Loading...

Loading...