Advanced-control timer (TIM1) RM0453

808/1461 RM0453 Rev 1

25.4.11 TIM1 capture/compare enable register

(TIM1_CCER)

Address offset: 0x20

Reset value: 0x0000 0000

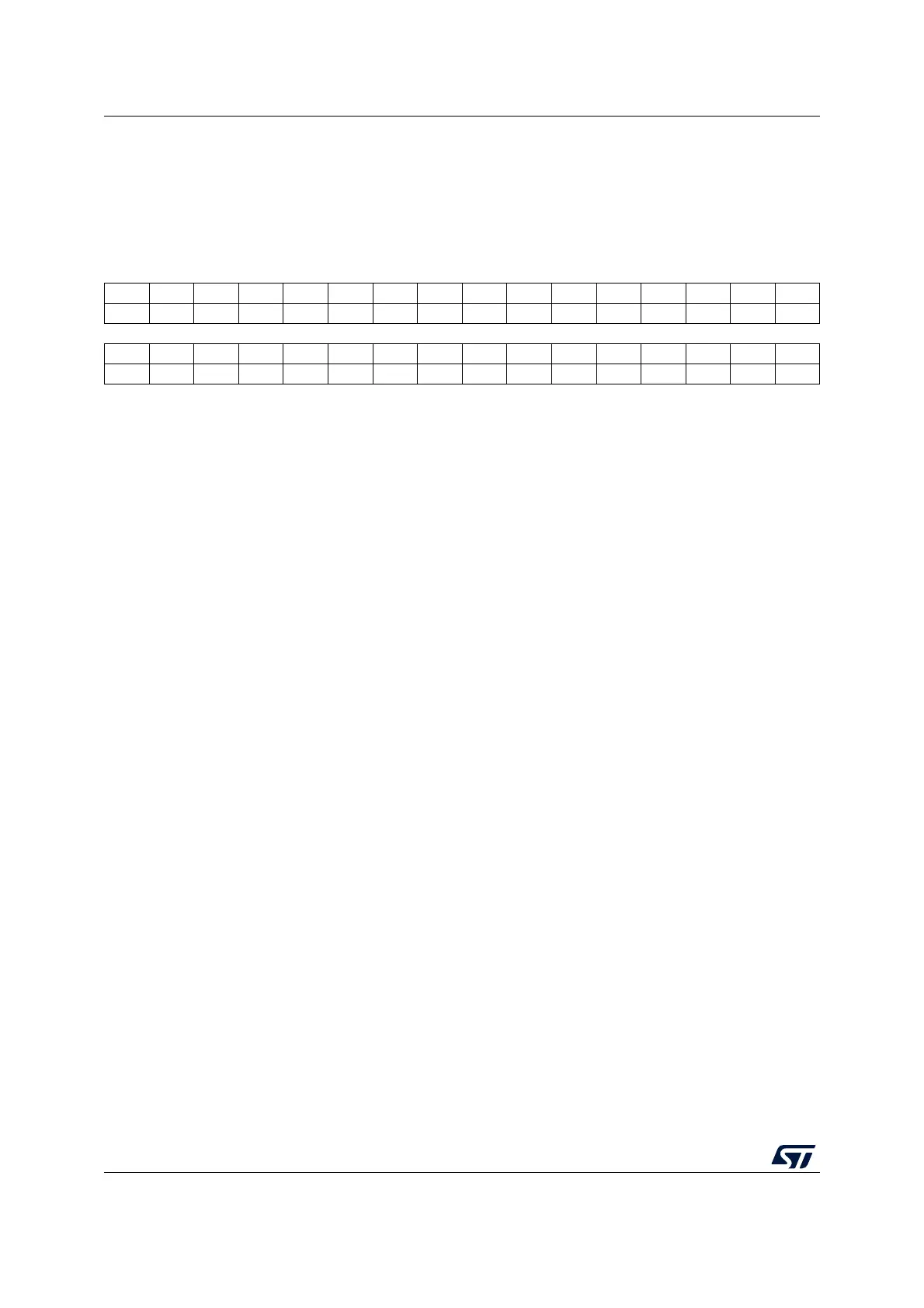

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CC6P CC6E Res. Res. CC5P CC5E

rw rw rw rw

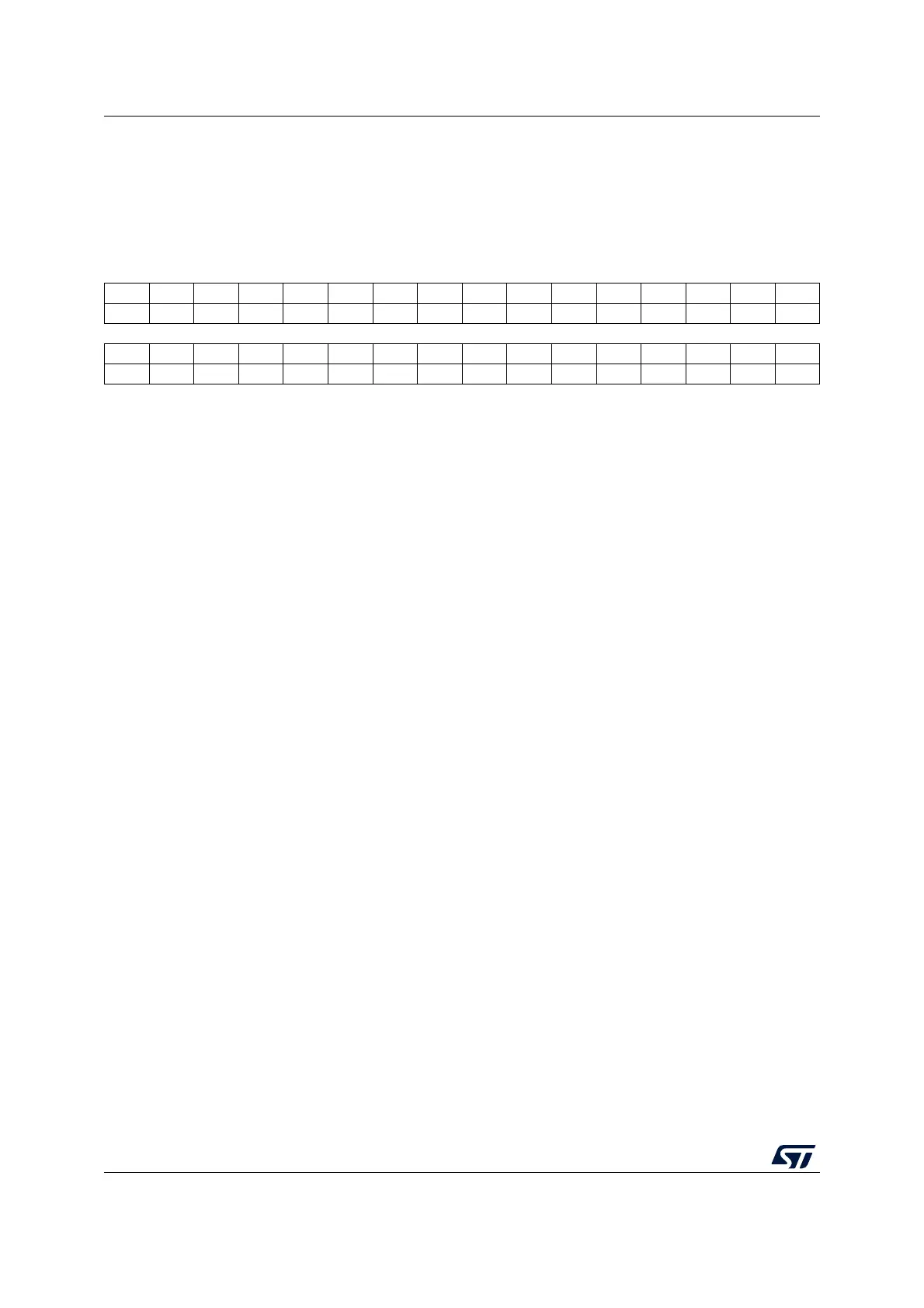

1514131211109876543210

CC4NP Res. CC4P CC4E CC3NP CC3NE CC3P CC3E CC2NP CC2NE CC2P CC2E CC1NP CC1NE CC1P CC1E

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bit 21 CC6P: Capture/Compare 6 output polarity

Refer to CC1P description

Bit 20 CC6E: Capture/Compare 6 output enable

Refer to CC1E description

Bits 19:18 Reserved, must be kept at reset value.

Bit 17 CC5P: Capture/Compare 5 output polarity

Refer to CC1P description

Bit 16 CC5E: Capture/Compare 5 output enable

Refer to CC1E description

Bit 15 CC4NP: Capture/Compare 4 complementary output polarity

Refer to CC1NP description

Bit 14 Reserved, must be kept at reset value.

Bit 13 CC4P: Capture/Compare 4 output polarity

Refer to CC1P description

Bit 12 CC4E: Capture/Compare 4 output enable

Refer to CC1E description

Bit 11 CC3NP: Capture/Compare 3 complementary output polarity

Refer to CC1NP description

Bit 10 CC3NE: Capture/Compare 3 complementary output enable

Refer to CC1NE description

Bit 9 CC3P: Capture/Compare 3 output polarity

Refer to CC1P description

Bit 8 CC3E: Capture/Compare 3 output enable

Refer to CC1E description

Bit 7 CC2NP: Capture/Compare 2 complementary output polarity

Refer to CC1NP description

Bit 6 CC2NE: Capture/Compare 2 complementary output enable

Refer to CC1NE description

Loading...

Loading...