Low-power timer (LPTIM) RM0453

954/1461 RM0453 Rev 1

28.3 LPTIM implementation

Table 189 describes LPTIM implementation on STM32WL5x devices. The full set of

features is implemented in LPTIM1. LPTIM2 and LPTIM3 support a smaller set of features,

but is otherwise identical to LPTIM1.

28.4 LPTIM functional description

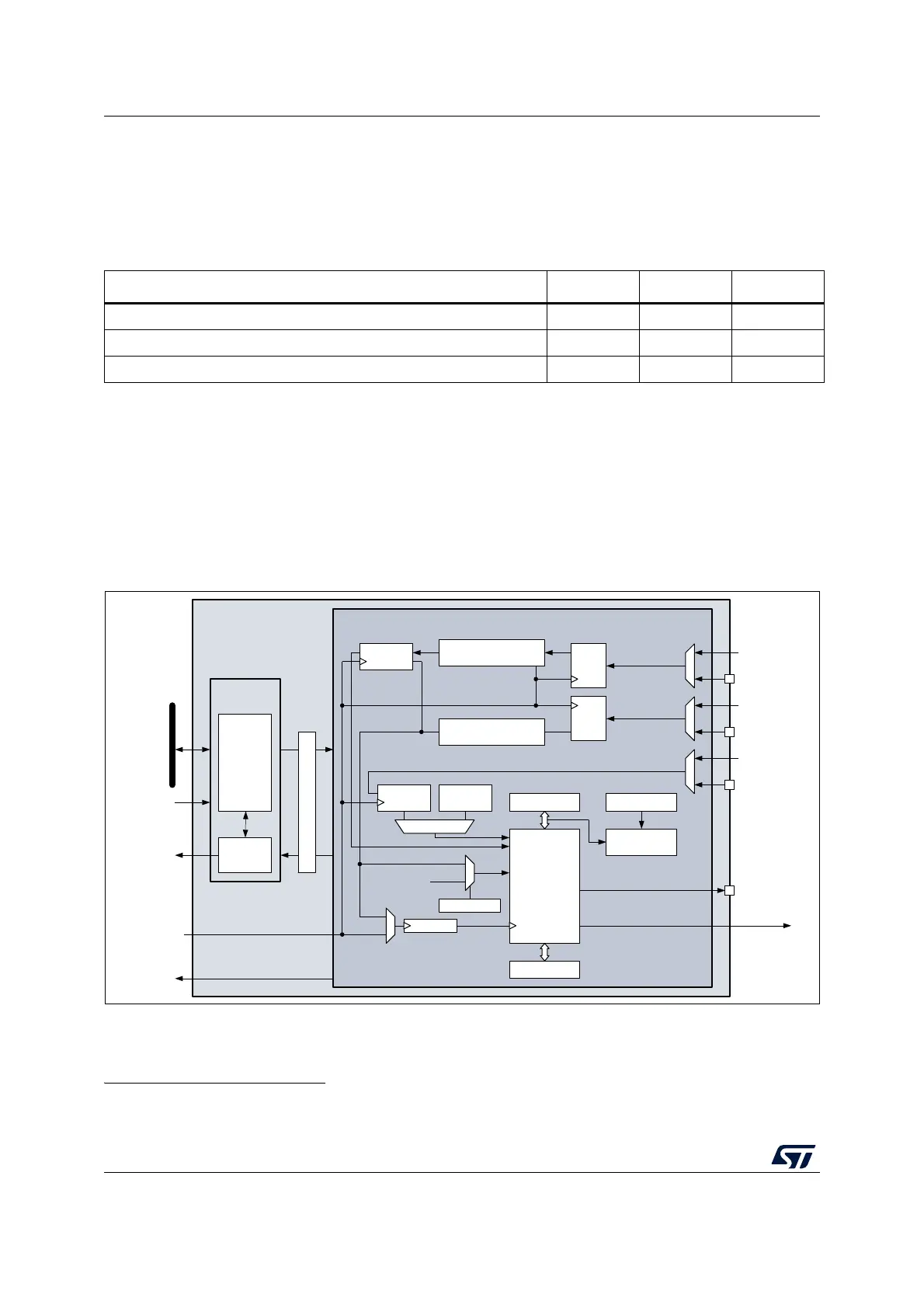

28.4.1 LPTIM block diagram

Figure 261. Low-power timer block diagram

(a)

1. lptim_out is the internal LPTIM output signal that can be connected to internal peripherals.

Table 189. STM32WL5x LPTIM features

LPTIM modes/features

(1)

LPTIM1 LPTIM2 LPTIM3

Encoder mode X - -

External input clock X X X

Wakeup from Stop

(2) (3) (3)

1. X = supported.

2. Wakeup supported from Stop 0, Stop 1 and Stop 2 modes.

3. Wakeup supported from Stop 0 and Stop 1 modes.

a. LPTIM2/LPTIM3 has only the input channel 1, no input channel 2.

MSv47413V3

LPTIM

Kernel clock domain

IRQ

interface

LPTIM

register

interface

APB clock

domain

32-bit APB bus

Wakeup

APB clock

LPTIM

interrupt

CLKMUX

16-bit counter

Count mode

16-bit compare

Repetition

counter

Prescaler

1

0

1

1

0

LPTIM_OUT

lptim_out

(1)

Synchronzation

16-bit ARR LPTIM_RCR

Mux trigger

Glitch

filter

CNTSTRT/

SNGSTRT

Glitch

filter

LPTIM_IN1

Encoder

Up/down

LPTIM_IN2

lptim_in2

lptim_in1

Glitch

filter

LPTIM_ETR

lptim_ext_trigx

Edge detector

Edge detector

lptim_ker_ck

Loading...

Loading...