RM0453 Rev 1 601/1461

RM0453 Digital-to-analog converter (DAC)

618

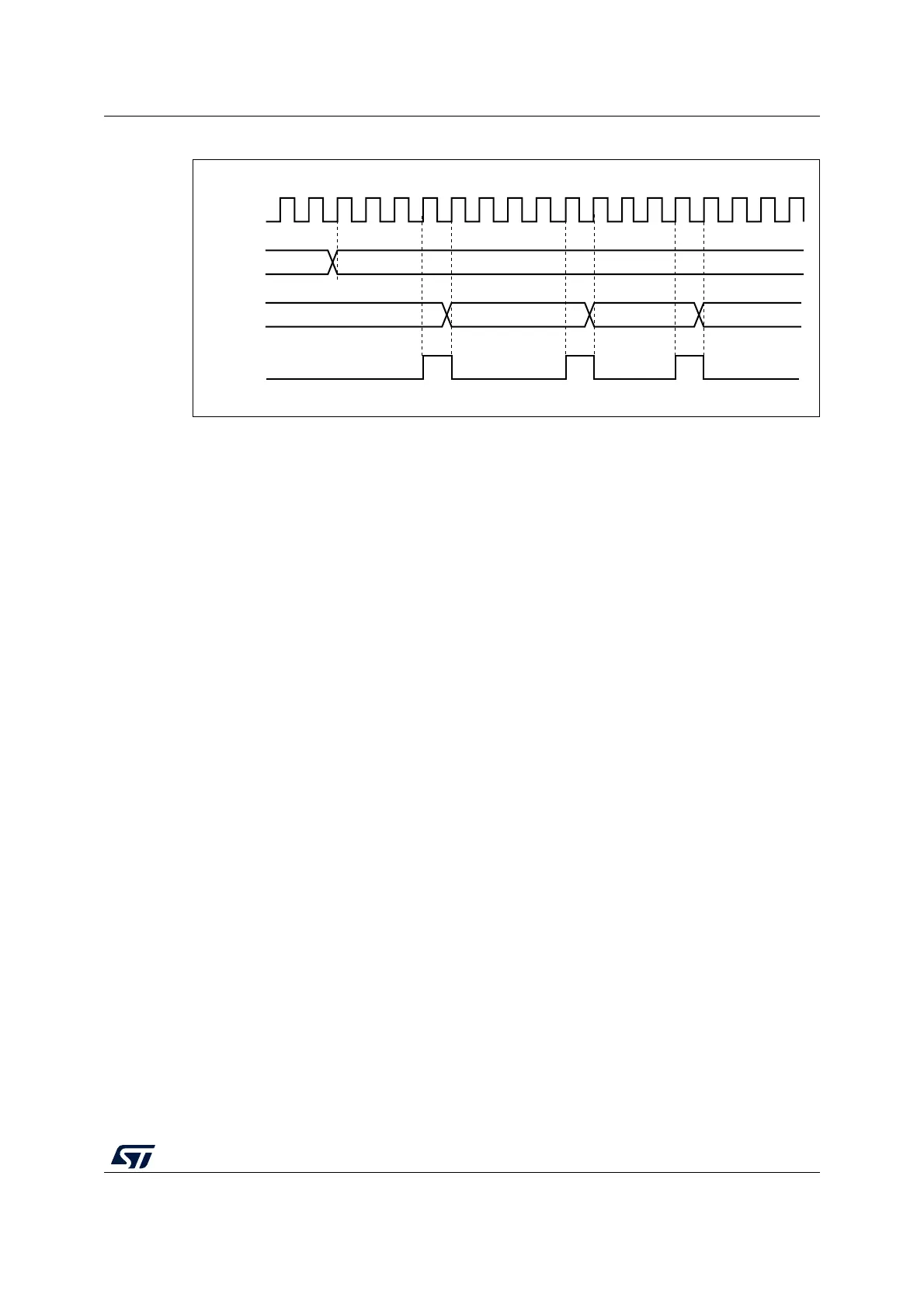

Figure 92. DAC conversion (SW trigger enabled) with triangle wave generation

Note: The DAC trigger must be enabled for triangle wave generation by setting the TEN1 bit in the

DAC_CR register.

The MAMP1[3:0] bits must be configured before enabling the DAC, otherwise they cannot

be changed.

19.4.11 DAC channel modes

The DAC channel can be configured in Normal mode or Sample and hold mode. The output

buffer can be enabled to allow a high drive capability. Before enabling output buffer, the

voltage offset needs to be calibrated. This calibration is performed at the factory (loaded

after reset) and can be adjusted by software during application operation.

Normal mode

In Normal mode, there are four combinations, by changing the buffer state and by changing

the DACx_OUT1 pin interconnections.

To enable the output buffer, the MODE1[2:0] bits in DAC_MCR register must be:

• 000: DAC is connected to the external pin

• 001: DAC is connected to external pin and to on-chip peripherals

To disable the output buffer, the MODE1[2:0] bits in DAC_MCR register must be:

• 010: DAC is connected to the external pin

• 011: DAC is connected to on-chip peripherals

Sample and hold mode

In Sample and hold mode, the DAC core converts data on a triggered conversion, and then

holds the converted voltage on a capacitor. When not converting, the DAC cores and buffer

are completely turned off between samples and the DAC output is tri-stated, therefore

reducing the overall power consumption. A stabilization period, which value depends on the

buffer state, is required before each new conversion.

In this mode, the DAC core and all corresponding logic and registers are driven by the LSI

low-speed clock (dac_hold_ck) in addition to the dac_pclk clock, allowing to use the DAC

channel in deep low power modes such as Stop mode.

The LSI low-speed clock (dac_hold_ck) must not be stopped when the Sample and hold

mode is enabled.

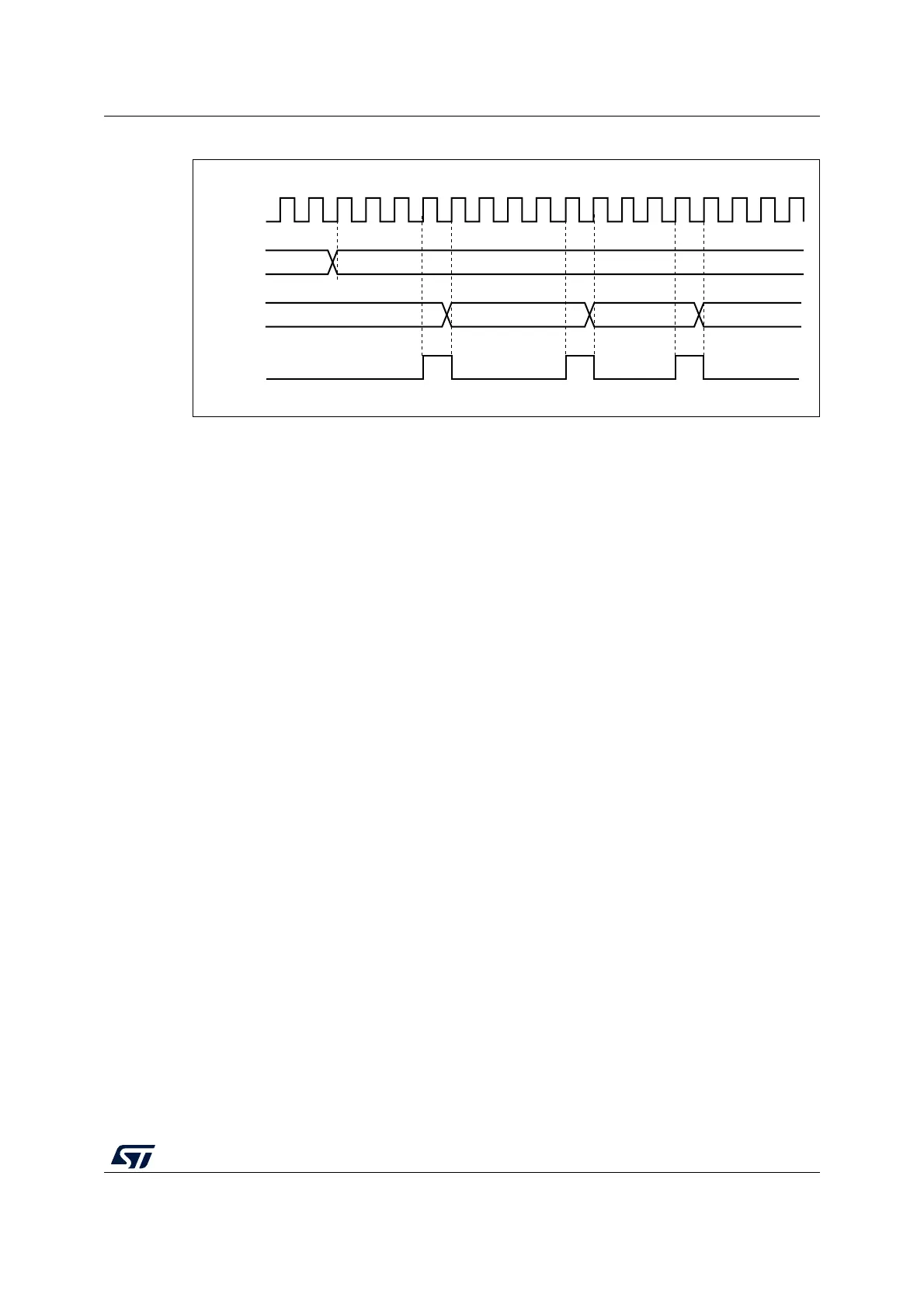

MS45321V1

dac_pclk

0xABE

0xABE

DHR

DOR

0xABF

SWTRIG

0xAC0

Loading...

Loading...