RM0453 Rev 1 1335/1461

RM0453 Debug support (DBG)

1448

38.4.3 DP control and status register (DP_CTRLSTATR)

Address offset: 0x04

and DP_SELECTR.DPBANKSEL = 0

Reset value: 0x0000 0000

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 ORUNERRCLR: overrrun error clear

0: No effect

1: Clears DP_CTRLSTATR.STICKYORUN bit.

Bit 3 WDERRCLR: write data error clear

0: No effect

1: Clears DP_CTRLSTATR.WDATAERR bit.

Bit 2 STKERRCLR: sticky error clear

0: No effect

1: Clears DP_CTRLSTATR.STICKYERR bit.

Bit 1 STKCMPCLR: sticky compare clear

0: No effect

1: Clears DP_CTRLSTATR.STICKYCMP bit

Bit 0 DAPABORT: data AP abort

Aborts current AP transaction if an excessive number of WAIT responses are returned,

indicating that the transaction is stalled.

0: No effect

1: Aborts the transaction.

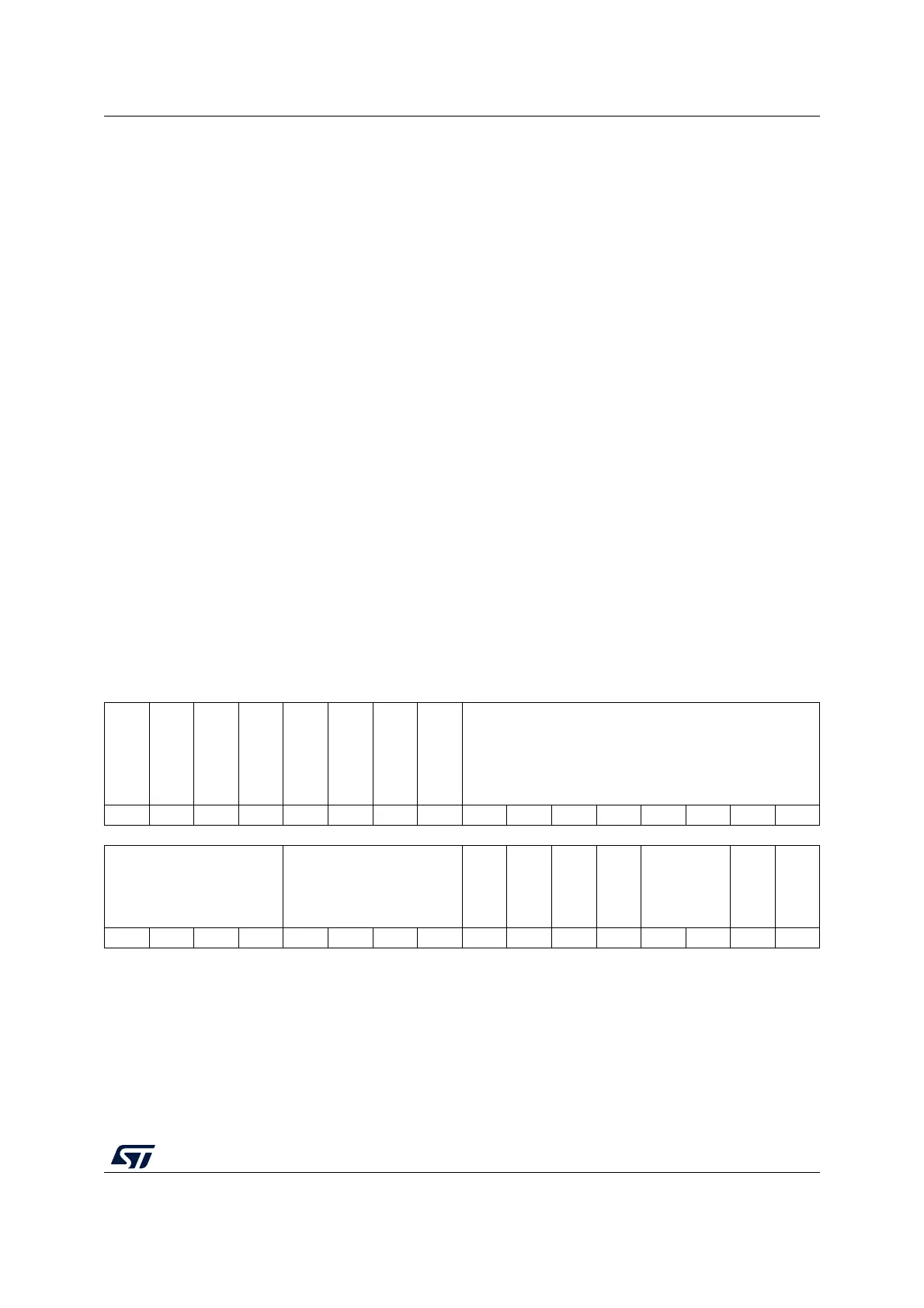

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res.

CDBGPWRUPACK

CDBGPWRUPREQ

Res. Res. Res. Res. TRNCNT[11:4]

rr rrrrrrrr

1514131211109876543210

TRNCNT[3:0] MASKLANE[3:0]

WDATAERR

READOK

STICKYERR

STICKYCMP

TRNMODE[1:0]

STICKYORUN

ORUNDETECT

rrrrrrrrrrrc_w1rc_w1rrrc_w1r

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 CDBGPWRUPACK: see description in Section 38.3.7

0 = DAPCLK gated

1 = DAPCLK enabled

Loading...

Loading...