Embedded Flash memory (FLASH) RM0453

106/1461 RM0453 Rev 1

change due to Flash operation requests by the other CPU, to limit the risk of receiving

a bus error when starting page erase).

3. Check and clear all error programming flags due to a previous programming. If not,

PGSERR is set.

4. Set PER and select the page to erase (PNB[6:0]) in FLASH_CR or FLASH_C2CR.

5. Set STRT in FLASH_CR or FLASH_C2CR.

6. Wait for BSY to be cleared in FLASH_SR or FLASH_C2SR.

Note: The internal oscillator HSI16 (16 MHz) is enabled automatically when the STRT bit is set,

and disabled automatically when the STRT bit is cleared, except if the HSI16 is previously

enabled with HSION in the RCC_CR register.

Flash mass erase

A user Flash memory mass erase requested by the CPU1 is only performed when the

system is non-secure (ESE = 0). When the system is secure (ESE = 1), a Flash memory

mass erase by the CPU1 is ignored and an illegal access event is generated.

When PCROP or WRP is enabled, any Flash memory mass erase is aborted and no erase

started.

Hide protection area and hide protection

area disable provide no protection for mass erase.

To perform a mass erase, follow the steps detailed below:

1. Check that no Flash memory operation is ongoing by checking BSY in FLASH_SR or

FLASH_C2SR.

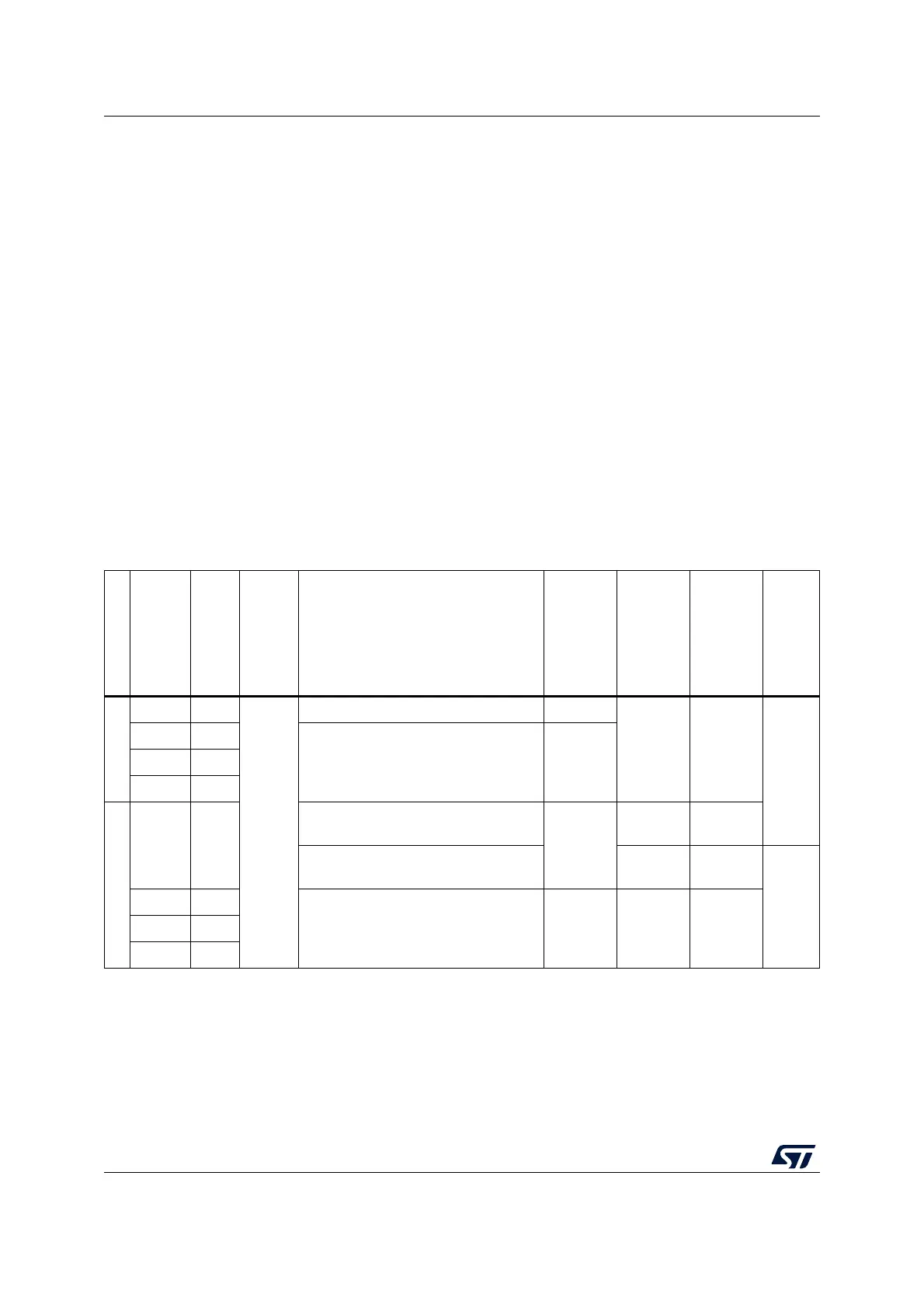

Table 14. Mass erase overview

ESE

PCROP WRP

PCROP

_RDP

Comment WRPERR

CPU1

bus error

CPU2

bus error

Illegal

access

event

0

No No

x

Memory is erased No

No No

No

No Yes

Erase aborted (no erase started) YesYes No

Yes Yes

1

No No

Requested by secure CPU2. The

Flash memory is mass erased.

No

N/A No

Requested by CPU1. Mass erase

aborted (no erase started)

No N/A

Yes

(1)

No Yes

Erase aborted (no erase started) Yes

(2)

No NoYes No

Yes Yes

1. When MER requested by the non-secure CPU1.

2. When requested by a secure bus master. When requested by a non-secure bus master, no WRPERR is generated and an

illegal access event is generated instead.

Loading...

Loading...