Debug support (DBG) RM0453

1408/1461 RM0453 Rev 1

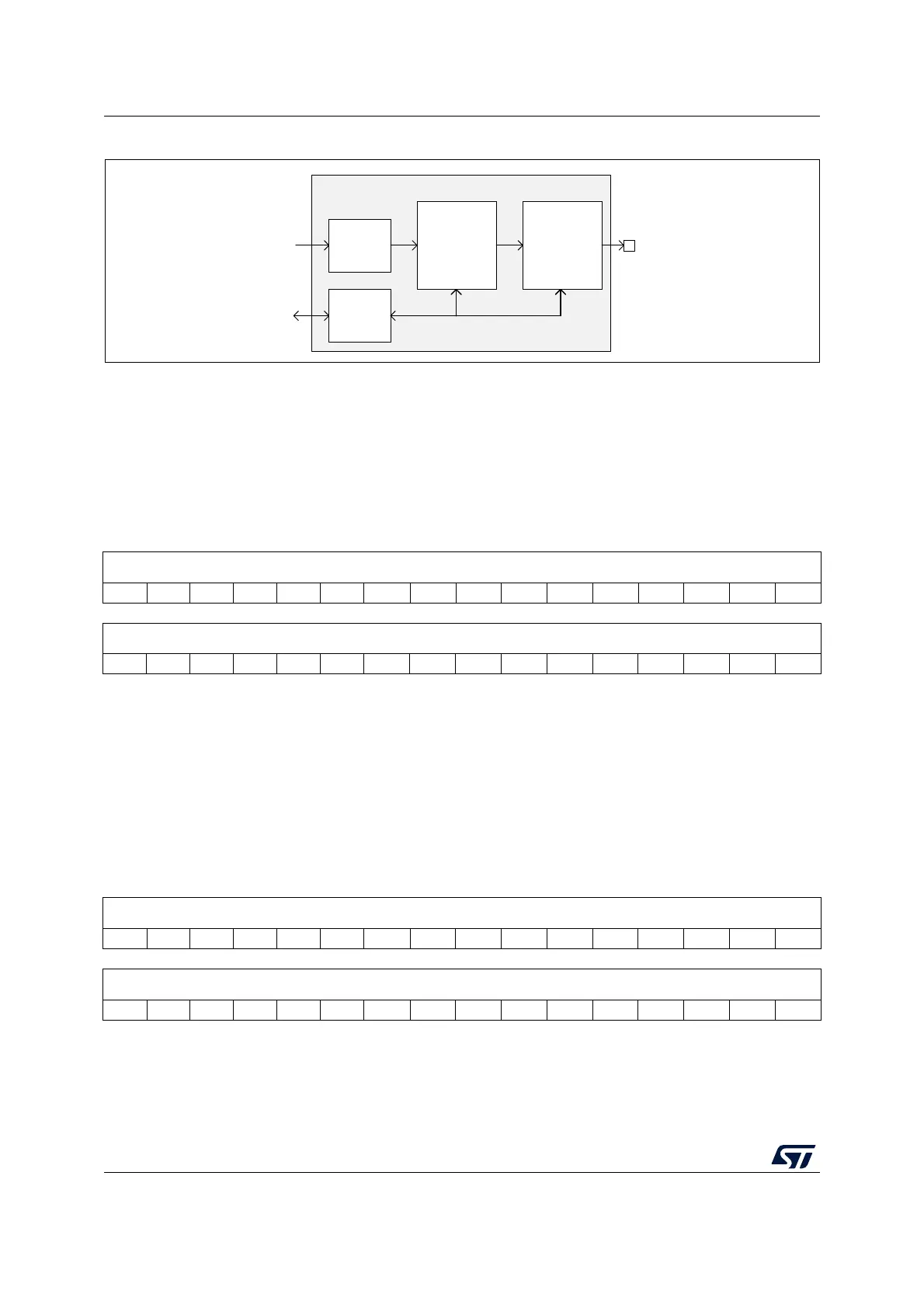

Figure 391. TPIU architecture

For more information on the TPIU, refer to the Arm

®

CoreSight™ SoC-400 Technical

Reference Manual [2.].

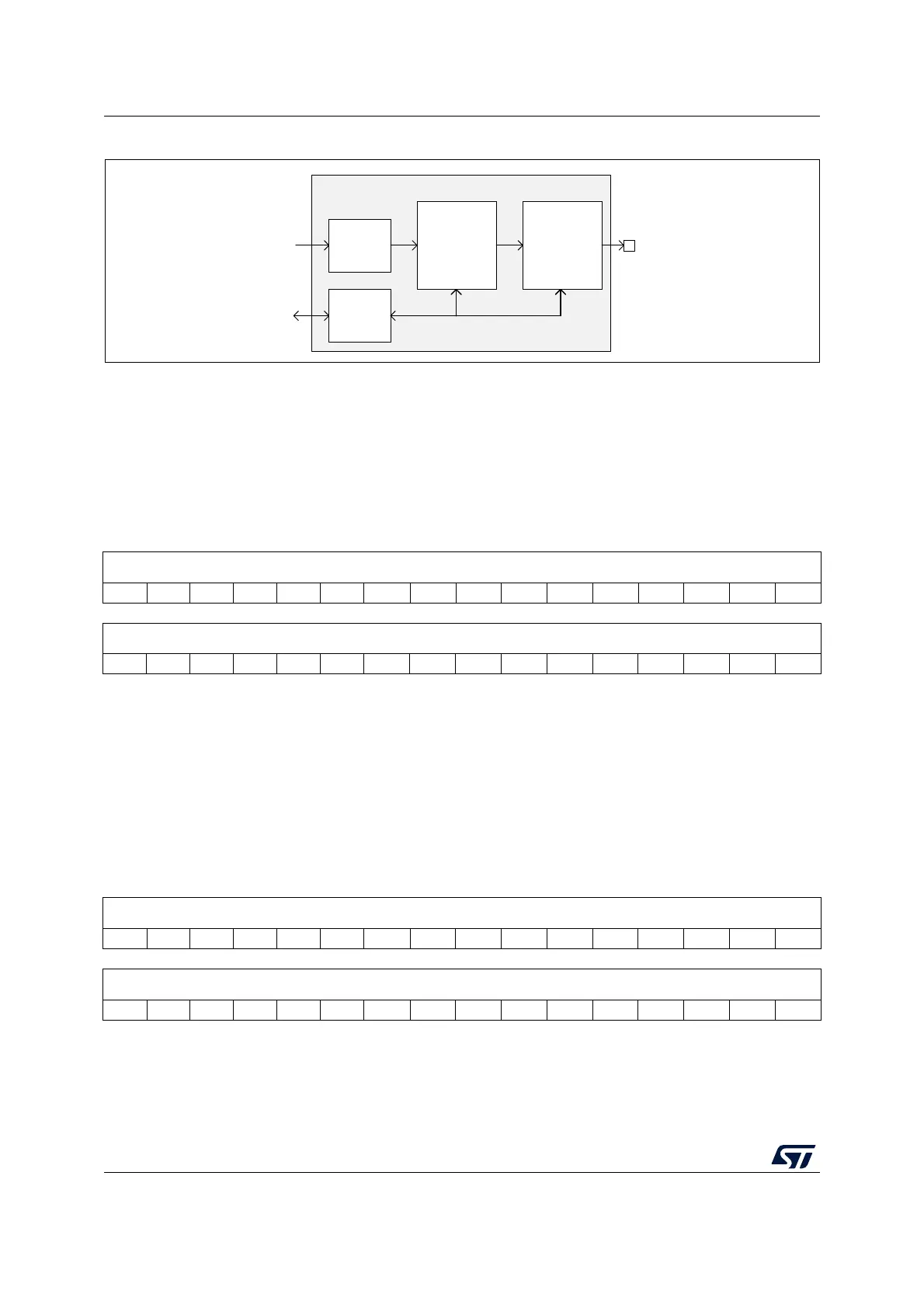

38.11.1 TPIU supported port size register (TPIU_SSPSR)

Address offset: 0x000

Reset value: 0x0000 000F

38.11.2 TPIU current port size register (TPIU_CSPSR)

Address offset: 0x004

Reset value: 0x0000 0001

MSv60741V1

TPIU

Trace

output

(serializer)

ITM ATB

PPB

TRACESWO

APB

interface

Formatter

ATB

interface

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PORTSIZE[31:16]

rrrrrr r r r r rrrrrr

1514131211109876543210

PORTSIZE[15:0]

rrrrrr r r r r rrrrrr

Bits 31:0 PORTSIZE[31:0]: supported trace port sizes, from 1 to 32 pins

Bit n-1 when set indicates that port size n is supported.

0x0000 000F: Port sizes 1 to 4 supported

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PORTSIZE[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

PORTSIZE[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 PORTSIZE[31:0]: current trace port size

Bit n-1 when set indicates that the current port size is n pins. The value of n must be within

the range of supported port sizes (1-4). Only one bit can be set, or unpredictable behaviour

may result. This register must be modified only when the formatter is stopped.

Loading...

Loading...