RM0453 Rev 1 1339/1461

RM0453 Debug support (DBG)

1448

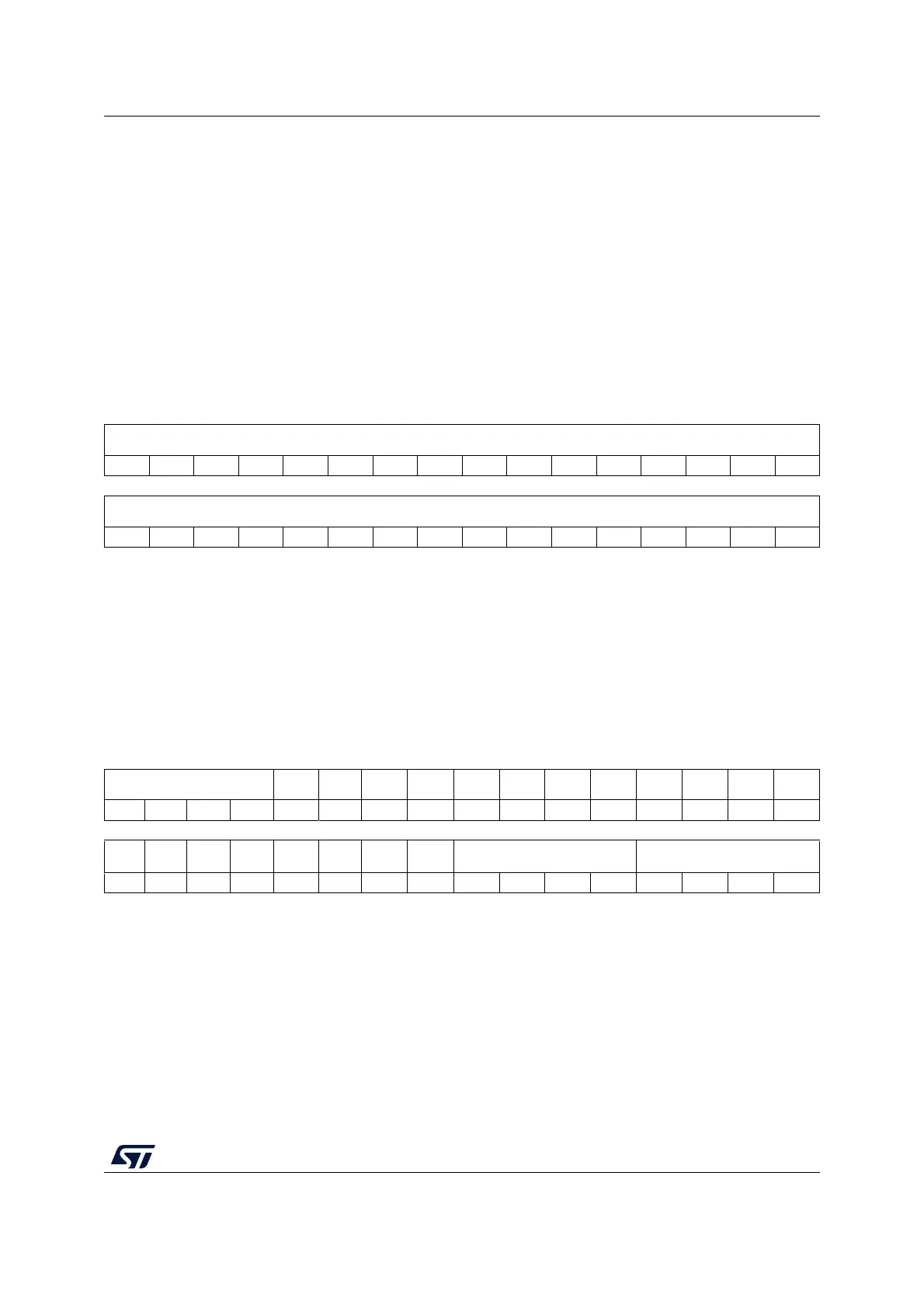

38.4.7 DP resend register (DP_RESENDR)

Address offset: 0x08

Reset value: 0x0000 0000

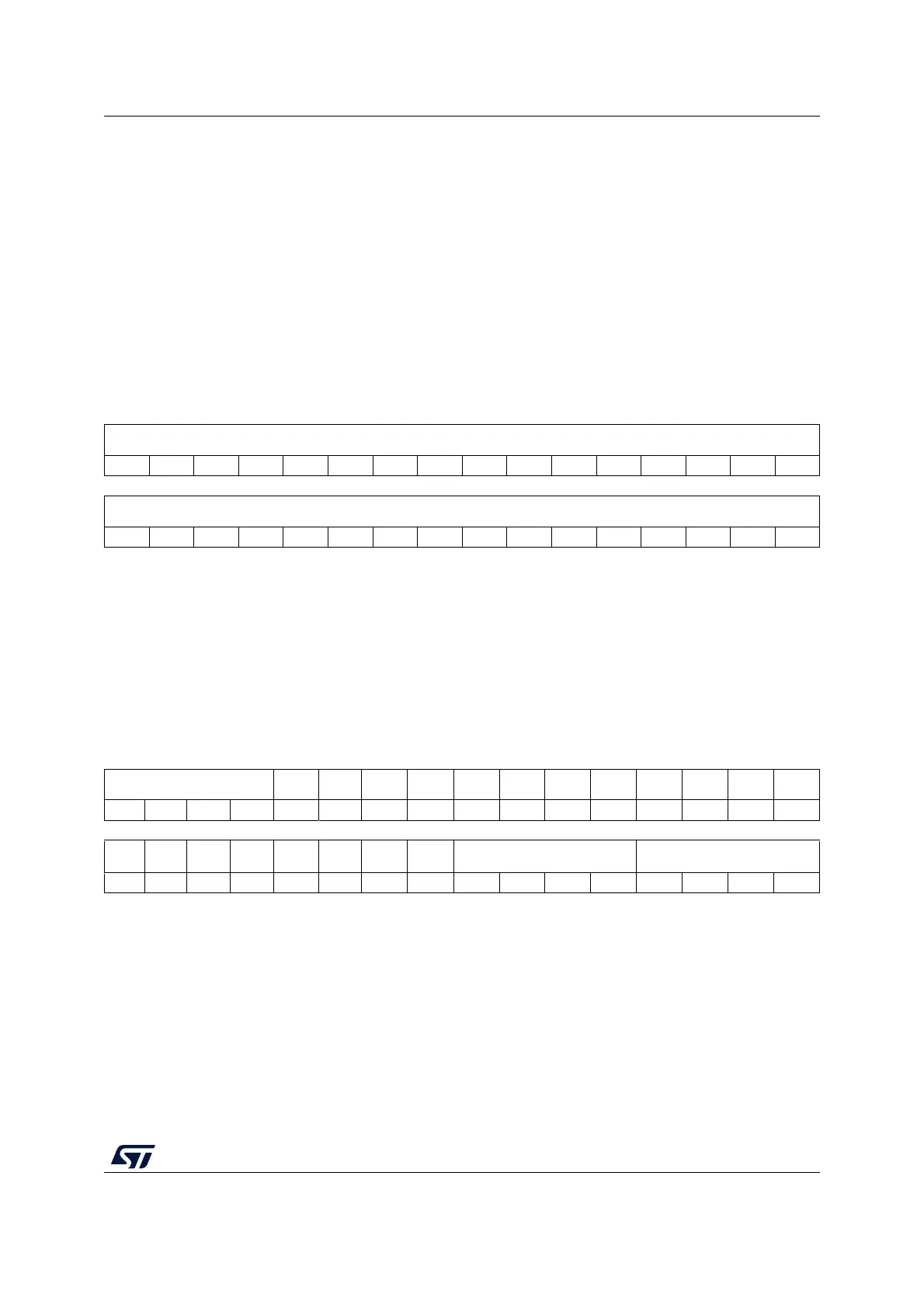

38.4.8 DP access port select register (DP_SELECTR)

Address offset: 0x08

Reset value: 0xXXXX XXXX

Bits 31:28 TINSTANCE[3:0]: target instance number

Defines the instance number for this device in a multi-drop system.

0x0: Instance number 0

Bits 27:4 Reserved, must be kept at reset value.

Bits 3:0 PROTSVN[3:0]: Serial-wire debug protocol version

0x1: Version 2

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RESEND[31:16]

rrrrrrrrrrrrrrrr

1514131211109876543210

RESEND[15:0]

rrrrrrrrrrrrrrrr

Bits 31:0 RESEND[31:0]: Returns the value that was returned by the last AP read or DP_RDBUFFR

read.

Used in the event of a corrupted read transfer.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

APSEL[3:0] Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ww w w

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. APBANKSEL[3:0] DPBANKSEL[3:0]

wwwwwwww

Bits 31:28 APSEL[3:0]: access port selection

Selects the access port for the next transaction.

0x0: AP0 - CPU1 (Cortex-M4) debug access port (AHB-AP)

0x1: AP1 - CPU2 (Cortex-M0+) debug access port (AHB-AP)

0x2 to 0xF: reserved

Loading...

Loading...