Debug support (DBG) RM0453

1392/1461 RM0453 Rev 1

Refer to Section 38.8: CPU1 ROM table for the register boundary addresses.

38.9 CPU1 breakpoint unit (FPB)

The FPB allows the user to set hardware breakpoints. It contains six comparators that

monitor the instruction fetch address and two literal address comparators.

If a match occurs, the address is remapped to an address in system memory, defined by the

FPB_REMAPR register plus an offset corresponding to the matching comparator.

Alternatively, the instruction comparators can be configured to generate a breakpoint

instruction.

38.9.1 FPB control register (FPB_CTRLR)

Address offset: 0x000

Reset value: 0x0000 0260

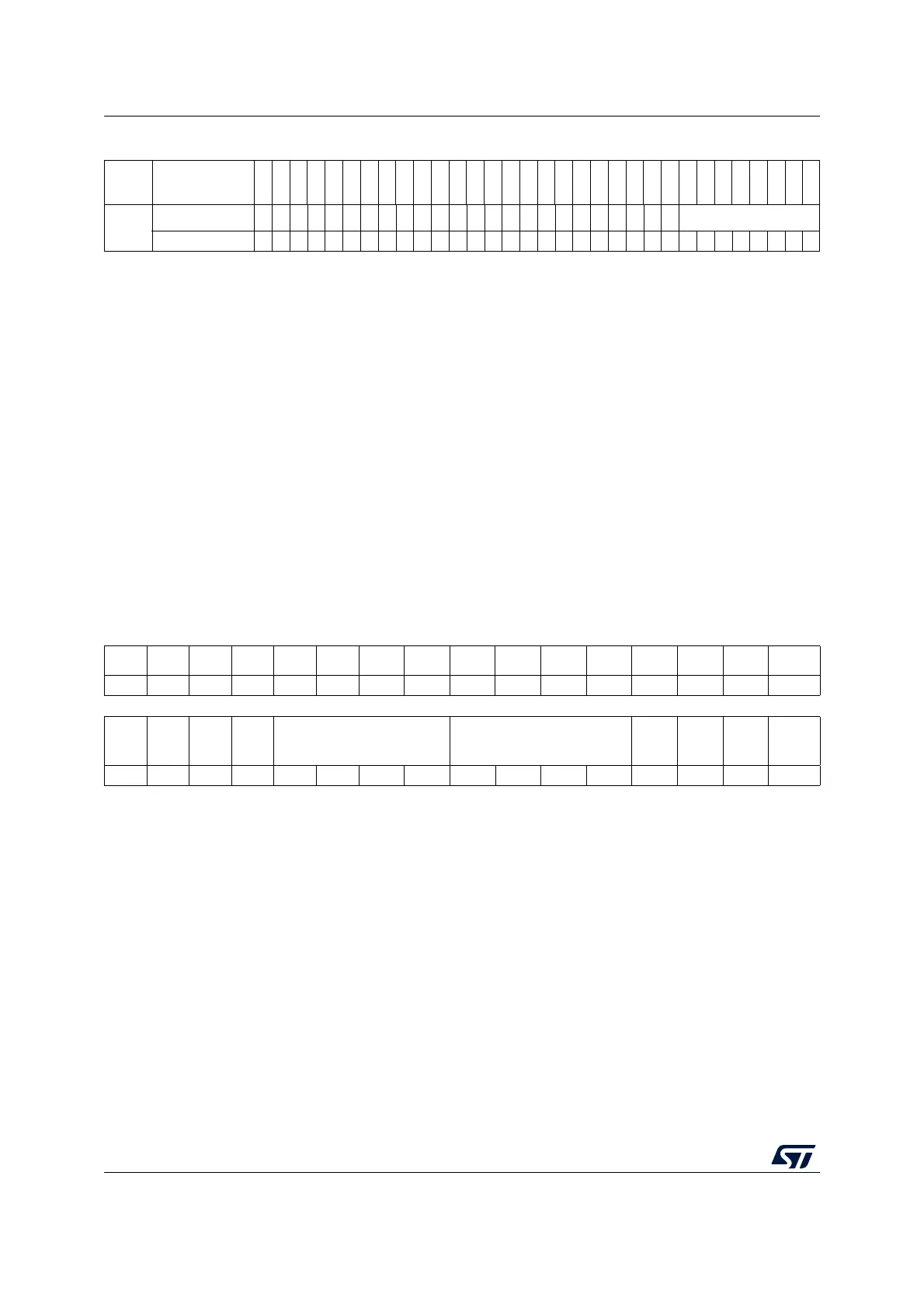

0xFFC

ROM_CIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[27:20]

Reset value 10110001

Table 278. CPU1 ROM table register map and reset values (continued)

Offset Register name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

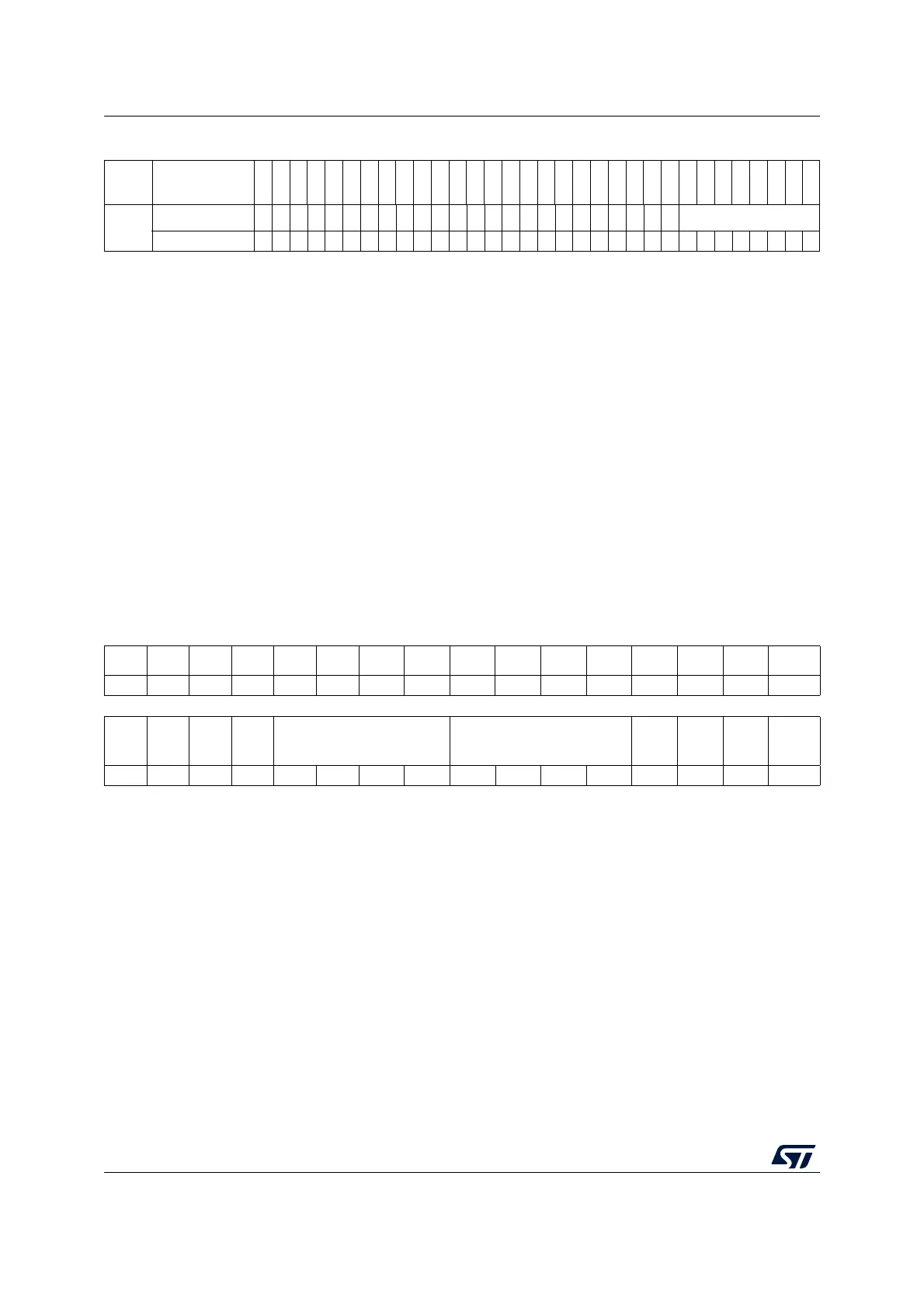

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res.

NUM_

CODE

6

NUM_

CODE

5

NUM_

CODE

4

NUM_LIT[3:0] NUM_CODE[3:0]

Res. Res.

KEY ENABLE

rrrrr r r r r r r rwrw

Bits 31:15 Reserved, must be kept at reset value.

Bits 11:8 NUM_LIT[3:0]: number of literal address comparators supported (read only)

0x2: Two literal comparators supported.

Bits 14, 13, 12, 7, 6,

5, 4

NUM_CODE[6:0]: number of instruction address comparators supported - least significant bits

(read only)

0x6: 6 instruction comparators supported

Bits 3:2 Reserved, must be kept at reset value.

Bit 1 KEY: write protect key

A write to FPB_CTRLR register is ignored if this bit is not set to 1.

Bit 0 ENABLE: FPB enable

0: Disabled

1: Enabled

Loading...

Loading...